Technologie MOS 6502

La technologie MOS 6502 (généralement prononcée “soixante-cinq-oh-deux” ou “six-cinq-oh-deux”) [3] est un microprocesseur 8 bits qui a été conçu par une petite équipe dirigée par Chuck Peddle pour la technologie MOS . L’équipe de conception avait auparavant travaillé chez Motorola sur le projet Motorola 6800 ; le 6502 est essentiellement une version simplifiée, moins chère et plus rapide de cette conception.

Un processeur MOS Technology 6502 dans un boîtier en plastique DIP-40 . Le code de date à quatre chiffres indique qu’il a été fabriqué au cours de la 45e semaine (novembre) de 1985. Un processeur MOS Technology 6502 dans un boîtier en plastique DIP-40 . Le code de date à quatre chiffres indique qu’il a été fabriqué au cours de la 45e semaine (novembre) de 1985. |

|

| informations générales | |

|---|---|

| Lancé | 1975 ; il y a 47 ans ( 1975 ) |

| Fabricant(s) commun(s) |

|

| Performance | |

| Max. Fréquence d’horloge du processeur | 1 MHz à 3 MHz |

| Largeur des données | 8 |

| Largeur d’adresse | 16 |

| Architecture et classement | |

| Jeu d’instructions | MOS 6502 |

| Des instructions | 56 |

| Spécifications physiques | |

| Transistors |

|

| Paquets) |

|

| Histoire | |

| Prédécesseur |

|

| Successeur |

|

Lors de son lancement en 1975, le 6502 était de loin le microprocesseur le moins cher du marché. Il s’est initialement vendu pour moins d’un sixième du coût des conceptions concurrentes de grandes entreprises, telles que le 6800 ou Intel 8080 . Son introduction a entraîné une baisse rapide des prix sur l’ensemble du marché des processeurs. Avec le Zilog Z80 , il a déclenché une série de projets qui ont abouti à la révolution de l’ ordinateur domestique au début des années 1980.

Les consoles de jeux vidéo et les ordinateurs populaires , tels que l’ Atari 2600 , la famille Atari 8 bits , Apple II , Nintendo Entertainment System , Commodore 64 , Atari Lynx , BBC Micro et autres, utilisent le 6502 ou des variantes de la conception de base. Peu de temps après l’introduction du 6502, la technologie MOS a été achetée par Commodore International , qui a continué à vendre le microprocesseur et les licences à d’autres fabricants. Au début du 6502, il a été acheté par Rockwell et Synertek , puis licencié à d’autres sociétés.

En 1981, le Western Design Center a commencé le développement d’une version CMOS , le 65C02 . Cela continue d’être largement utilisé dans les systèmes embarqués , avec des volumes de production estimés à des centaines de millions. [4]

Histoire et utilisation

Origines chez Motorola

Carte de démonstration Motorola 6800 construite par Chuck Peddle et John Buchanan en 1974

Carte de démonstration Motorola 6800 construite par Chuck Peddle et John Buchanan en 1974

Le 6502 a été conçu par bon nombre des mêmes ingénieurs qui avaient conçu la famille de microprocesseurs Motorola 6800 . [5] Motorola a lancé le projet de microprocesseur 6800 en 1971 avec Tom Bennett comme architecte principal. La disposition des puces a commencé à la fin de 1972, les premières puces 6800 ont été fabriquées en février 1974 et la famille complète a été officiellement publiée en novembre 1974. [6] [7] John Buchanan était le concepteur de la puce 6800 [8] [9] et Rod Orgill, qui a ensuite réalisé le 6501, a aidé Buchanan dans les analyses de circuit et la disposition des puces. [10] Bill Mensch a rejoint Motorola en juin 1971 après avoir obtenu son diplôme de l’Université d’Arizona (à 26 ans). [11]Sa première mission a été d’aider à définir les circuits intégrés périphériques pour la famille 6800 et plus tard, il a été le principal concepteur de l’ adaptateur d’interface périphérique 6820 (PIA). [12] Les ingénieurs de Motorola pourraient exécuter des simulations analogiques et numériques sur un ordinateur central IBM 370-165 . [13] Bennett a embauché Chuck Peddle en 1973 pour effectuer un travail de soutien architectural sur les produits de la famille 6800 déjà en cours. [14] Il a contribué dans de nombreux domaines, y compris la conception du 6850 ACIA (interface série). [15]

Les clients cibles de Motorola étaient des sociétés d’électronique établies telles que Hewlett-Packard , Tektronix , TRW et Chrysler . [16] En mai 1972, les ingénieurs de Motorola ont commencé à rendre visite à des clients sélectionnés et à partager les détails de leur système de microprocesseur 8 bits proposé avec des interfaces ROM, RAM, parallèle et série. [17]Au début de 1974, ils ont fourni des échantillons d’ingénierie des puces afin que les clients puissent prototyper leurs conceptions. La stratégie de “famille de produits totale” de Motorola ne s’est pas concentrée sur le prix du microprocesseur, mais sur la réduction du coût total de conception du client. Ils ont proposé un logiciel de développement sur un ordinateur en temps partagé, le système de débogage “EXORciser”, une formation sur site et un support technique pour les ingénieurs d’application sur le terrain. [18] [19] Intel et Motorola avaient initialement annoncé un prix de 360 $ pour un seul microprocesseur. [20] [21] Le prix réel des quantités produites était bien inférieur. Motorola a proposé un kit de conception contenant le 6800 avec six puces de support pour 300 $. [22]

Peddle, qui accompagnait les vendeurs lors des visites chez les clients, a constaté que les clients étaient rebutés par le coût élevé des puces à microprocesseur. [23] Dans le même temps, ces visites aboutissaient invariablement aux ingénieurs qu’il présentait à produire des listes d’instructions requises beaucoup plus petites que “toutes ces instructions fantaisistes” qui avaient été incluses dans le 6800. [24] Peddle et d’autres membres de l’équipe a commencé à décrire la conception d’un microprocesseur amélioré et de taille réduite. À cette époque, la nouvelle usine de fabrication de semi-conducteurs de Motorola à Austin, au Texas, avait du mal à produire des puces MOS, et le milieu de 1974 marqua le début d’une récession d’un an dans l’industrie des semi-conducteurs. En outre, de nombreux habitants de Mesa, en Arizonales employés étaient mécontents de la prochaine relocalisation à Austin, au Texas . [25]

La direction de la division des produits semi-conducteurs de Motorola a été submergée de problèmes et n’a montré aucun intérêt pour la proposition de microprocesseur à faible coût de Peddle. Finalement, Peddle a reçu une lettre officielle lui disant d’arrêter de travailler sur le système. [26] Peddle a répondu à l’ordre en informant Motorola que la lettre représentait une déclaration officielle “d’abandon de projet”, et en tant que telle, la propriété intellectuelle qu’il avait développée jusque-là était désormais la sienne. [27]Dans une interview de novembre 1975, le président de Motorola, Robert Galvin, a finalement convenu que le concept de Peddle était bon et que la division avait raté une opportunité, “Nous n’avons pas choisi les bons leaders dans la division des produits semi-conducteurs.” La division a été réorganisée et la direction remplacée. Le nouveau vice-président du groupe, John Welty, a déclaré : « L’organisation des ventes de semi-conducteurs a perdu sa sensibilité aux besoins des clients et n’a pas pu prendre de décisions rapides. [28]

Technologie MOS

Une publicité de 1973 MOS Technology mettant en évidence leurs capacités de circuits intégrés personnalisés

Une publicité de 1973 MOS Technology mettant en évidence leurs capacités de circuits intégrés personnalisés

MOS Technology MCS6501, dans un boîtier en céramique blanche, fabriqué fin août 1975

MOS Technology MCS6501, dans un boîtier en céramique blanche, fabriqué fin août 1975

Peddle a commencé à chercher en dehors de Motorola une source de financement pour ce nouveau projet. Il a d’abord approché le PDG de Mostek , LJ Sevin , mais il a refusé. Sevin a admis plus tard que c’était parce qu’il avait peur que Motorola les poursuive en justice. [29]

Alors que Peddle rendait visite à Ford Motor Company lors d’un de ses voyages de vente, Bob Johnson, plus tard chef de la division d’automatisation des moteurs de Ford, a mentionné que leur ancien collègue John Paivinen était passé à General Instrument et avait appris par lui-même la conception de semi-conducteurs. [30] Paivinen a ensuite formé MOS Technology à Valley Forge, Pennsylvanie en 1969 avec deux autres cadres de General Instrument, Mort Jaffe et Don McLaughlin. Allen-Bradley , un fournisseur de composants électroniques et de commandes industrielles, a acquis une participation majoritaire en 1970. [31] La société a conçu et fabriqué des circuits intégrés personnalisés pour les clients et avait développé une gamme de puces de calcul. [32]

Après l’échec des efforts de Mostek, Peddle a approché Paivinen, qui “l’a immédiatement compris”. [33] Le 19 août 1974, Chuck Peddle, Bill Mensch, Rod Orgill, Harry Bawcom, Ray Hirt, Terry Holdt et Wil Mathys ont quitté Motorola pour rejoindre MOS. Mike Janes a rejoint plus tard. Sur les dix-sept concepteurs de puces et responsables de la mise en page de l’équipe 6800, huit sont partis. L’objectif de l’équipe était de concevoir et de produire un microprocesseur à faible coût pour les applications embarquées et de cibler une clientèle aussi large que possible. Cela ne serait possible que si le microprocesseur était peu coûteux et que l’équipe fixait l’objectif de prix à 5 $ en volume. [34] Mensch a déclaré plus tard que l’objectif n’était pas le prix du processeur lui-même, mais de créer un ensemble de puces qui pourraient se vendre à 20 $.pour concurrencer l’ Intel 4040 récemment introduit qui s’est vendu 29 $ dans un chipset complet similaire. [35]

Les puces sont produites en imprimant plusieurs copies de la conception de la puce sur la surface d’une “wafer” , un Disque mince de silicium très pur. Des puces plus petites peuvent être imprimées en plus grand nombre sur la même plaquette, ce qui diminue leur prix relatif. De plus, les tranches comprennent toujours un certain nombre de minuscules défauts physiques dispersés sur la surface. Toute puce imprimée à cet endroit échouera et devra être jetée. Des puces plus petites signifient qu’une seule copie est moins susceptible d’être imprimée sur un défaut. Pour ces deux raisons, le coût du produit final dépend fortement de la taille de la conception de la puce. [36]

Les puces 6800 d’origine étaient destinées à être180 mils × 180 mils [a] (4,6 mm × 4,6 mm) , mais la mise en page a été achevée à212 mils × 212 mils (5,4 mm × 5,4 mm) , soit une surface de 29,0 mm 2 . [37] Pour la nouvelle conception, l’objectif de coût exigeait un objectif de taille de153 mils × 168 mils (3,9 mm × 4,3 mm) , ou une zone de16,6 mm 2 . [38] Plusieurs nouvelles techniques seraient nécessaires pour atteindre cet objectif.

Passer au NMOS

Deux avancées importantes sont arrivées sur le marché au moment de la conception du 6502, ce qui a permis de réduire considérablement les coûts. Le premier était le passage au NMOS à charge d’épuisement . Le 6800 utilisait un processus NMOS précoce qui nécessitait trois tensions d’alimentation, mais l’une des caractéristiques de la puce était un doubleur de tension intégré qui permettait d’utiliser une seule alimentation + 5 V pour + 5, -5 et + 12 V en interne, par opposition à d’autres. puces de l’époque comme l’ Intel 8080 qui nécessitait trois broches d’alimentation distinctes. [39]Bien que cette fonctionnalité réduise la complexité de l’alimentation et de la disposition des broches, elle nécessitait toujours des rails d’alimentation séparés pour les différentes portes de la puce, ce qui augmentait la complexité et la taille. En passant à la nouvelle conception de charge d’épuisement, une seule alimentation +5 V était tout ce qui était nécessaire, éliminant toute cette complexité. [40]

Un autre avantage pratique était que le signal d’horloge des processeurs antérieurs devait être suffisamment puissant pour survivre à toute la dissipation lors de son parcours dans les circuits, ce qui nécessitait presque toujours une puce externe séparée pouvant fournir un signal puissant. Avec les besoins en énergie réduits de NMOS, l’horloge pourrait être déplacée sur la puce, simplifiant la conception globale de l’ordinateur. Ces changements ont considérablement réduit la complexité et le coût de mise en œuvre d’un système complet. [40]

Un autre changement qui se produisait était l’introduction du masquage de projection. Auparavant, les puces étaient modelées sur la surface de la plaquette en plaçant un masque sur la surface de la plaquette, puis en faisant briller une lumière vive dessus. Les masques ramassaient souvent de minuscules morceaux de saleté ou de résine photosensible lorsqu’ils étaient retirés de la puce, provoquant des défauts à ces endroits lors de tout masquage ultérieur. Avec des conceptions complexes comme les processeurs, 5 ou 6 étapes de masquage de ce type seraient utilisées, et la probabilité qu’au moins une de ces étapes introduise un défaut était très élevée. Dans la plupart des cas, 90 % de ces conceptions étaient défectueuses, ce qui a donné un rendement de 10 %. Le prix des exemplaires fonctionnels devait couvrir le coût de production des 90% jetés. [41]

En 1973, Perkin-Elmer a introduit le système Micraligne , qui projetait une image du masque sur la plaquette au lieu d’exiger un contact direct. Les masques ne ramassaient plus la saleté des plaquettes et duraient de l’ordre de 100 000 utilisations au lieu de 10. Cela a éliminé les échecs étape par étape et les taux de défauts élevés autrefois observés sur les conceptions complexes. Les rendements sur les CPU ont immédiatement bondi de 10% à 60 ou 70%. Cela signifiait que le prix du processeur avait diminué à peu près du même montant et que le microprocesseur était soudainement devenu un appareil de base. [41]

Les lignes de fabrication existantes de MOS Technology étaient basées sur l’ancienne technologie PMOS, elles n’avaient pas encore commencé à travailler avec NMOS lorsque l’équipe est arrivée. Paivinen a promis d’avoir une ligne NMOS en place et en cours d’exécution à temps pour commencer la production du nouveau CPU. Il a tenu sa promesse, la nouvelle ligne était prête en juin 1975. [42]

Notes de conception

Chuck Peddle, Rod Orgill et Wil Mathys ont conçu l’architecture initiale des nouveaux processeurs. Un article de septembre 1975 dans le magazine EDN donne ce résumé de la conception : [43]

La famille MOS Technology 650X représente une tentative consciente de huit anciens employés de Motorola qui ont travaillé sur le développement du système 6800 pour sortir une pièce qui remplacerait et surpasserait le 6800, tout en le sous-vendant. Avec le recul acquis sur le projet 6800, l’équipe MOS Technology dirigée par Chuck Peddle, a apporté les modifications architecturales suivantes au processeur Motorola…

Le principal changement en termes de taille de puce a été l’élimination des pilotes à trois états des sorties du bus d’adresse. Cela avait été inclus dans le 6800 pour lui permettre de fonctionner avec d’autres puces dans des rôles d’accès direct à la mémoire (DMA) et de co-traitement, au prix d’un espace de puce important. En pratique, l’utilisation d’un tel système exigeait que les autres appareils soient tout aussi complexes, et les concepteurs avaient plutôt tendance à utiliser des systèmes hors puce pour coordonner cet accès. Le 6502 a simplement supprimé cette fonctionnalité, conformément à sa conception en tant que contrôleur peu coûteux utilisé pour des tâches spécifiques et communiquant avec des appareils simples. Peddle a suggéré que toute personne ayant réellement besoin de ce style d’accès puisse l’implémenter avec un seul 74158 . [44] [c]

La différence majeure suivante était de simplifier les registres. Pour commencer, l’un des deux accumulateurs a été retiré. Les registres à usage général tels que les accumulateurs doivent être accessibles par de nombreuses parties du Décodeur d’instructions et nécessitent donc des quantités importantes de câblage pour déplacer les données vers et depuis leur stockage. Deux accumulateurs facilitent de nombreuses tâches de codage, mais coûtent à la conception de la puce elle-même une complexité importante. [43] D’autres économies ont été réalisées en réduisant le registre de pile de 16 à 8 bits, ce qui signifie que la pile ne pouvait avoir que 256 octets de long, ce qui était suffisant pour son rôle prévu en tant que microcontrôleur. [43]

Le registre d’index IX 16 bits a été divisé en deux, devenant X et Y. Plus important encore, le style d’accès a changé; dans le 6800, IX détenait une adresse de 16 bits, qui était compensée par un nombre de 8 bits fourni avec l’instruction, les deux ont été ajoutés pour produire l’adresse finale. Dans le 6502 (et la plupart des autres conceptions), l’adresse de base 16 bits était stockée dans l’instruction, et le X ou Y y était ajouté. [44]

Enfin, le jeu d’instructions a été simplifié, libérant de la place dans le décodeur et la logique de contrôle. Sur les 72 instructions originales du 6800, 56 restaient. Parmi celles supprimées figuraient toute instruction qui déplaçait des données entre les deux accumulateurs du 6800, ainsi qu’un certain nombre d’instructions de branchement inspirées du PDP-11 , comme la possibilité de comparer directement deux valeurs numériques. Le 6502 utilisait un système plus simple qui gérait les comparaisons en effectuant des calculs sur l’accumulateur, puis en examinant les indicateurs de résultat. [44]

La conception de haut niveau de la puce a dû être transformée en dessins de transistors et d’interconnexions. Chez MOS Technology, la “mise en page” était un processus très manuel réalisé avec des crayons de couleur et du papier vélin . La mise en page se composait de milliers de formes polygonales sur six dessins différents; un pour chaque couche du processus de fabrication. Compte tenu des limites de taille, l’ensemble de la conception de la puce devait être constamment pris en compte. Mensch et Paivinen ont travaillé sur le Décodeur d’instructions [46] tandis que Mensch, Peddle et Orgill ont travaillé sur l’ALU et les registres. Une autre avancée, développée lors d’une fête, était un moyen de partager une partie du câblage interne pour permettre de réduire la taille de l’ALU. [47]

Malgré tous leurs efforts, la conception finale a fini par être trop large de 5 mils. [48] Les 6502 premières puces mesuraient 168 × 183 mils (4,3 × 4,7 mm) , soit une surface de 19,8 mm 2 . L’instruction de rotation à droite (ROR) ne fonctionnait pas dans le premier silicium, donc l’instruction a été temporairement omise des documents publiés, mais la prochaine itération de la conception a rétréci la puce et corrigé l’instruction de rotation à droite, qui a ensuite été incluse dans la documentation révisée . [49]

Présentation des 6501 et 6502

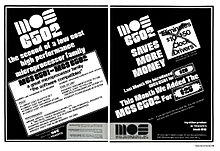

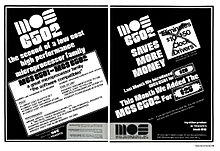

Publicité de présentation pour les microprocesseurs MOS Technology MCS6501 et MCS6502

Publicité de présentation pour les microprocesseurs MOS Technology MCS6501 et MCS6502

MOS introduirait deux microprocesseurs basés sur la même conception sous-jacente : le 6501 se brancherait sur la même prise que le Motorola 6800, tandis que le 6502 réorganiserait le brochage pour prendre en charge un oscillateur d’horloge sur puce. Les deux fonctionneraient avec d’autres puces de support conçues pour le 6800. Ils n’exécuteraient pas le logiciel 6800 car ils avaient un jeu d’instructions différent, des registres différents et principalement des modes d’adressage différents. [50] Rod Orgill était responsable de la conception 6501; il avait assisté John Buchanan chez Motorola sur le 6800. Bill Mensch a fait le 6502 ; il était le concepteur de l’adaptateur d’interface périphérique (PIA) 6820 chez Motorola. Harry Bawcom, Mike Janes et Sydney-Anne Holt ont aidé à la mise en page.

L’introduction du microprocesseur de MOS Technology était différente du lancement traditionnel du produit qui a duré plusieurs mois. La première série d’un nouveau circuit intégré est normalement utilisée pour des tests internes et partagée avec certains clients en tant qu'”échantillons d’ingénierie”. Ces puces ont souvent un ou deux défauts de conception mineurs qui seront corrigés avant le début de la production. L’objectif de Chuck Peddle était de vendre les premières puces 6501 et 6502 aux participants du salon Wescon à San Francisco à partir du 16 septembre 1975. Peddle était un porte-parole très efficace et les microprocesseurs MOS Technology étaient largement couverts dans la presse spécialisée. L’un des premiers était un article d’une page entière sur les microprocesseurs MCS6501 et MCS6502 dans le numéro du 24 juillet 1975 du magazine Electronics .EE Times (24 août 1975), [52] EDN (20 septembre 1975), Electronic News (3 novembre 1975), Byte (novembre 1975) [53] et Microcomputer Digest (novembre 1975). [54] Des publicités pour le 6501 sont apparues dans plusieurs publications la première semaine d’août 1975. Le 6501 serait en vente chez Wescon pour 20 $ chacun. [55] En septembre 1975, les publicités incluaient à la fois les microprocesseurs 6501 et 6502. Le 6502 ne coûterait que 25 $ (équivalent à 126 $ en 2021). [56]

Lorsque MOS Technology est arrivé à Wescon, ils ont constaté que les exposants n’étaient pas autorisés à vendre quoi que ce soit sur le salon. Ils ont loué la suite MacArthur à l’ hôtel St. Francis et y ont dirigé les clients pour qu’ils achètent les processeurs. Dans la suite, les processeurs étaient stockés dans de grands bocaux pour impliquer que les puces étaient en production et facilement disponibles. Les clients ne savaient pas que la moitié inférieure de chaque bocal contenait des copeaux non fonctionnels. [57] Les jetons coûtaient 20 $ et 25 $ , tandis que la trousse de documentation coûtait 10 $ supplémentaires . Les utilisateurs ont été encouragés à faire des photocopiesdes documents, un moyen peu coûteux pour MOS Technology de diffuser des informations sur les produits. Les fiches techniques préliminaires ne répertorient que 55 instructions, à l’exclusion de l’instruction Rotate Right (ROR) qui ne fonctionnait pas correctement sur ces premières puces. Les revues dans Byte et EDN ont noté l’absence de l’instruction ROR. La révision suivante de la mise en page a résolu ce problème et la fiche technique de mai 1976 répertorie 56 instructions. Peddle voulait que chaque ingénieur et amateur intéressé ait accès aux puces et à la documentation; d’autres sociétés de semi-conducteurs ne voulaient traiter qu’avec des clients “sérieux”. Par exemple, Signetics présentait le microprocesseur 2650 et ses publicités demandaient aux lecteurs d’écrire pour obtenir des informations sur l’en-tête de leur entreprise.[58]

MOS Technology MCS6502, dans un boîtier en céramique blanche, fabriqué fin 1975

MOS Technology MCS6502, dans un boîtier en céramique blanche, fabriqué fin 1975

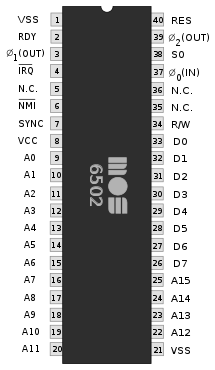

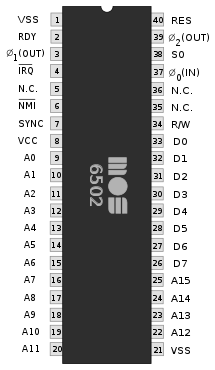

| Broche | 6800 | 6501 | 6502 |

|---|---|---|---|

| 2 | Arrêt | Prêt | Prêt |

| 3 | ∅1 (po) | ∅1 (po) | ∅1 (sortie) |

| 5 | Adresse mémoire valide | Adresse mémoire valide | NC |

| 7 | Autobus disponible | Autobus disponible | SYNCHRONISER |

| 36 | Activation du bus de données | Activation du bus de données | NC |

| 37 | ∅2 (po) | ∅2 (po) | ∅0 (po) |

| 38 | NC | NC | Définir l’indicateur de débordement |

| 39 | Contrôle à trois états | NC | ∅2 (sortie) |

Procès contre Motorola

La fiche technique de mai 1976 omettait le microprocesseur 6501 qui se trouvait dans la version d’ août 1975 .

La fiche technique de mai 1976 omettait le microprocesseur 6501 qui se trouvait dans la version d’ août 1975 .

L’introduction de 6501/6502 dans la presse et chez Wescon a été un énorme succès. L’inconvénient était que la couverture médiatique étendue a attiré l’attention de Motorola. En octobre 1975, Motorola a réduit le prix d’un seul microprocesseur 6800 de 175 $ à 69 $ . Le kit de conception du système de 300 $ a été réduit à 150 $ et il est désormais livré avec une carte de circuit imprimé. [59] Le 3 novembre 1975, Motorola a demandé une injonction à la Cour fédérale pour empêcher MOS Technology de fabriquer et de vendre des produits à microprocesseur. Ils ont également déposé une plainte pour contrefaçon de brevet et détournement de secrets commerciaux. Motorola a affirmé que sept anciens employés avaient rejoint MOS Technology pour créer les produits à microprocesseur de cette société. [60]

Motorola était une entreprise d’un milliard de dollars avec un cas plausible et des avocats. Le 30 octobre 1974, Motorola avait déposé de nombreuses demandes de brevet sur la famille des microprocesseurs et avait obtenu vingt-cinq brevets. Le premier était en juin 1976 et le second était à Bill Mensch le 6 juillet 1976, pour la configuration de la puce 6820 PIA. Ces brevets couvraient le bus 6800 et la manière dont les puces périphériques s’interfaçaient avec le microprocesseur. [61]Motorola a commencé à fabriquer des transistors en 1950 et possédait un portefeuille de brevets sur les semi-conducteurs. Allen-Bradley a décidé de ne pas lutter contre cette affaire et a revendu son intérêt pour la technologie MOS aux fondateurs. Quatre des anciens ingénieurs de Motorola ont été nommés dans le procès : Chuck Peddle, Will Mathys, Bill Mensch et Rod Orgill. Tous ont été nommés inventeurs dans les 6800 demandes de brevet. Au cours du processus de découverte, Motorola a découvert qu’un ingénieur, Mike Janes, avait ignoré les instructions de Peddle et apporté ses 6800 documents de conception à MOS Technology. [62] En mars 1976, la technologie MOS désormais indépendante était à court d’argent et devait régler l’affaire. Ils ont accepté d’abandonner le processeur 6501, de payer 200 $ à Motorola000 et retourner les documents qui, selon Motorola, étaient confidentiels. Les deux sociétés ont convenu d’ accorder des licences croisées sur les brevets des microprocesseurs. [63] En mai, Motorola a baissé le prix d’un seul microprocesseur 6800 à 35 $ . En novembre, Commodore avait acquis la technologie MOS. [64] [65]

Ordinateurs et jeux

Avec des problèmes juridiques derrière eux, MOS se retrouvait toujours avec le problème d’amener les développeurs à essayer leur processeur, incitant Chuck Peddle à concevoir l’ ordinateur monocarte MDT-650 (“terminal de développement de micro-ordinateur”) . Un autre groupe au sein de l’entreprise a conçu le KIM-1 , qui a été vendu semi-complet et pourrait être transformé en un système utilisable avec l’ajout d’un terminal informatique tiers et d’un lecteur de cassette compact . À leur grand étonnement, le KIM-1 s’est bien vendu aux amateurs et aux bricoleurs, ainsi qu’aux ingénieurs auxquels il était destiné. Le Rockwell AIM 65 associésystème de contrôle/formation/développement a également bien fonctionné. Le logiciel de l’AIM 65 était basé sur celui du MDT. Un autre produit à peu près similaire était le Synertek SYM-1 .

L’une des premières utilisations “publiques” de la conception a été le micro- ordinateur Apple I , introduit en 1976. Le 6502 a ensuite été utilisé dans le Commodore PET et l ‘ Apple II , [66] tous deux sortis en 1977. Il a ensuite été utilisé dans l’ Atari Famille 8 bits et ordinateurs domestiques Acorn Atom , le BBC Micro , [66] Commodore VIC-20 et d’autres modèles à la fois pour les ordinateurs personnels et les entreprises, tels que Ohio Scientific et Oric . Le 6510 , un successeur direct du 6502 avec un port d’E/S numérique et un bus d’adresse à trois états , était le CPU utilisé dans l’ordinateur domestique le plus vendu [67] [68] Commodore 64 . Des processeurs de variante 6502 ou 6502 ont été utilisés dans tous les lecteurs de disquettes de Commodore pour tous leurs ordinateurs 8 bits, de la gamme PET (dont certains avaient deux processeurs basés sur 6502) jusqu’au Commodore 128D, y compris le Commodore 64, et dans tous les lecteurs de Disque d’Atari pour toute leur gamme d’ordinateurs 8 bits, du 400/800 au XEGS.

Une autre utilisation importante de la famille 6500 était dans les jeux vidéo. Le premier à utiliser la conception du processeur a été l’ Atari VCS , rebaptisé plus tard l ‘ Atari 2600 . Le VCS utilisait une variante du 6502 appelée 6507 , qui avait moins de broches et, par conséquent, ne pouvait adresser que 8 Ko de mémoire. Des millions de consoles Atari seraient vendues, chacune avec un processeur MOS. Une autre utilisation importante a été par le Nintendo Entertainment System et Famicom . Le 6502 utilisé dans la NES était une deuxième version source de Ricoh , un système partiel sur puce , dépourvu de la décimale codée en binairemode mais a ajouté 22 registres mappés en mémoire et du matériel sur puce pour la génération de sons, la lecture du joypad et la liste de sprites DMA . Appelé 2A03 sur les consoles NTSC et 2A07 sur les consoles PAL (la différence étant le rapport du diviseur de mémoire et une table de correspondance pour les fréquences d’échantillonnage audio), ce processeur a été produit exclusivement pour Nintendo . L’ Atari Lynx utilisait une version 4 MHz de la puce, la 65SC02 .

Dans les années 1980, un magazine d’électronique populaire Elektor/Elektuur a utilisé le processeur dans sa carte de développement de microprocesseur Junior Computer .

- Ordinateurs domestiques et consoles de jeux vidéo utilisant le 6502 ou ses variantes

-

![]()

![]()

Atome de gland

-

![]()

![]()

Électron de gland

-

![]()

![]()

Pomme je

-

![]()

![]()

Pomme II

-

![]()

![]()

Apple IIe

-

![]()

![]()

Atari 2600

-

![]()

![]()

Atari 5200

-

![]()

![]()

Atari 7800

-

![]()

![]()

Atari 800

-

![]()

![]()

Atari Lynx

-

![]()

![]()

Maître de la BBC

-

![]()

![]()

Micro BBC

-

![]()

![]()

Commodore PET

-

![]()

![]()

Commodore VIC-20

-

![]()

![]()

Commodore 64

-

![]()

![]()

Commodore 128

-

![]()

![]()

Ordinateur familial (Famicom)

-

![]()

![]()

Système de divertissement Nintendo

-

![]()

![]()

Ohio Scientific Challenger 4P

-

![]()

![]()

Orao

-

![]()

![]()

Orique-1

-

![]()

![]()

Oric Atmos

-

![]()

![]()

Animal de compagnie numérique Tamagotchi [69]

-

![]()

![]()

TurboGrafx-16

Description technique

Processeur 6502. La section régulière en haut est la ROM de décodage d’instructions, la section apparemment aléatoire au centre est la logique de contrôle, et en bas se trouvent les registres (à droite) et l’ALU (à gauche). Les connexions du bus de données se trouvent en bas à droite et le bus d’adresses en bas et en bas à gauche. [38]

Processeur 6502. La section régulière en haut est la ROM de décodage d’instructions, la section apparemment aléatoire au centre est la logique de contrôle, et en bas se trouvent les registres (à droite) et l’ALU (à gauche). Les connexions du bus de données se trouvent en bas à droite et le bus d’adresses en bas et en bas à gauche. [38]

Configuration 6502 broches ( DIP 40 broches ) Registres MOS 6502

Configuration 6502 broches ( DIP 40 broches ) Registres MOS 6502

| 1 5 | 1 4 | 1 3 | 1 2 | 1 1 | 1 0 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | (emplacement du bit) |

| Registres principaux | ||||||||||||||||

| UN | Un cumulateur | |||||||||||||||

| Registres d’index | ||||||||||||||||

| X | Indice X | |||||||||||||||

| Oui | Indice Y | |||||||||||||||

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 | PS | Pointeur de pile _ | |||||||

| Compteur de programme | ||||||||||||||||

| PC | Compteur de programmes _ | |||||||||||||||

| Registre d’état | ||||||||||||||||

| N | V | – | B | ré | je | Z | C | Drapeaux du processeur _ |

Le 6502 est un processeur little-endian 8 bits avec un bus d’adresse 16 bits . Les versions originales ont été fabriquées à l’aide d’une puce de technologie de processus de 8 μm [70] avec une taille de matrice de 3,9 mm × 4,3 mm (annoncée comme 153 mils × 168 mils ), pour une surface totale de 16,6 mm 2 . [38]

La logique interne fonctionne à la même vitesse que la fréquence d’horloge externe, mais malgré les faibles vitesses d’horloge (généralement de l’ordre de 1 à 2 MHz ), les performances du 6502 étaient compétitives avec d’autres processeurs contemporains utilisant des horloges nettement plus rapides. Cela est en partie dû à une simple machine à états implémentée par une logique combinatoire (sans horloge) dans une plus grande mesure que dans de nombreuses autres conceptions; l’horloge biphasée (fournissant deux synchronisations par cycle) pourrait ainsi contrôler directement le cycle de la machine. Les instructions typiques peuvent prendre deux fois moins de cycles pour terminer sur le 6502 que sur les conceptions contemporaines. Comme la plupart des CPU simples de l’époque, la puce dynamique NMOS 6502 n’est pas séquencée par une ROM à microcode [clarification nécessaire ]mais utilise unPLA(qui occupait environ 15% de la surface de la puce) pour le décodage et le séquençage des instructions. Comme dans la plupart des microprocesseurs 8 bits, la puce effectue un chevauchement limité de la récupération et de l’exécution.

La faible fréquence d’horloge a modéré les exigences de vitesse de la mémoire et des périphériques connectés au processeur, car seulement environ 50% du cycle d’horloge était disponible pour l’accès à la mémoire (en raison de la conception asynchrone, cette fraction variait fortement selon les versions de puce). C’était essentiel à une époque où la mémoire abordable avait des temps d’accès compris entre 250 et 450 ns .

Étant donné que la puce n’accédait à la mémoire que pendant certaines parties du cycle d’horloge et que ces cycles étaient indiqués par la broche de sortie PHI2-low, d’autres puces d’un système pouvaient accéder à la mémoire pendant les périodes où le 6502 était hors du bus. Cela était parfois appelé “accès caché”. Cette technique était largement utilisée par les systèmes informatiques; ils utiliseraient une mémoire capable d’accéder à 2 MHz, puis exécuteraient le processeur à 1 MHz. Cela garantissait que le processeur et le matériel vidéo pouvaient entrelacer leurs accès, avec une performance totale correspondant à celle du périphérique de mémoire. [71] Lorsque des mémoires plus rapides sont devenues disponibles dans les années 1980, les nouvelles machines pouvaient fonctionner à des fréquences d’horloge plus élevées, comme le processeur 2 MHz du BBC Micro , et continuer à utiliser les techniques de partage de bus.

Registres

Comme son prédécesseur, le 6800, le 6502 a très peu de registres . Les registres du 6502 comprennent un registre d’ accumulateur 8 bits (A), deux Registres d’index 8 bits (X et Y), 7 bits d’indicateur d’état du processeur (P ; du bit 7 au bit 0, ce sont le négatif (N), le débordement ( V), réservé , pause (B), décimal (D), désactivation d’interruption (I), zéro (Z) et indicateur de report (C)), un Pointeur de pile 8 bits (S) et un compteur de programme 16 bits (PC). [72] Cela se compare à une conception typique de la même époque, le Z80, qui possède huit registres 8 bits à usage général, qui peuvent être combinés en quatre registres 16 bits. Le Z80 disposait également d’un ensemble complet de registres alternatifs, ce qui faisait un total de seize registres à usage général.

Afin de compenser quelque peu le manque de registres, le 6502 comprenait un mode d’adressage de page zéro qui utilise un octet d’adresse dans l’instruction au lieu des deux nécessaires pour adresser le plein64 Ko de mémoire. Cela permet d’accéder rapidement au premier256 octets de RAM en utilisant des instructions plus courtes. Chuck Peddle a déclaré dans des interviews que l’intention spécifique était de permettre à ces premiers256 octets de RAM à utiliser comme registres. [ citation nécessaire ]

L’espace d’adressage de la pile est câblé à la page mémoire $01, c’est-à-dire la plage d’adresses $0100– $01FF( 256– 511). L’accès logiciel à la pile se fait via quatre instructions de mode d’adressage implicite, dont les fonctions sont de pousser ou de faire sauter (tirer) l’accumulateur ou le registre d’état du processeur. La même pile est également utilisée pour les appels de sous-programme via les instructions JSR (saut au sous-programme) et RTS (retour du sous-programme) et pour la gestion des interruptions .

Adressage

La puce utilise efficacement les Registres d’index et de pile avec plusieurs modes d’adressage , y compris un mode rapide “page directe” ou “page zéro”, similaire à celui trouvé sur le PDP-8 , qui accède aux emplacements mémoire des adresses 0 à 255 avec un seul Adresse 8 bits (enregistrant le cycle normalement requis pour récupérer l’octet de poids fort de l’adresse) – le code du 6502 utilise la page zéro tout comme le code des autres processeurs utiliserait des registres. Sur certains micro-ordinateurs basés sur 6502 avec un système d’exploitation, le système d’exploitation utilise la majeure partie de la page zéro, ne laissant qu’une poignée d’emplacements pour l’utilisateur.

Les modes d’adressage incluent également des instructions implicites (instructions à 1 octet); absolu (3 octets) ; indexé absolu (3 octets) ; page zéro indexée (2 octets); relatif (2 octets); accumulateur (1); indirect,x et indirect,y (2); et immédiat(2). Le mode absolu est un mode à usage général. Les instructions de branchement utilisent un décalage signé de 8 bits par rapport à l’instruction après le branchement ; la plage numérique -128..127 se traduit donc par 128 octets en arrière et 127 octets en avant à partir de l’instruction suivant la branche (qui est de 126 octets en arrière et 129 octets en avant depuis le début de l’instruction de branche). Le mode Accumulateur utilise l’accumulateur comme adresse effective et n’a besoin d’aucune donnée d’ opérande . Le mode immédiat utilise un opérande littéral 8 bits .

Adressage indirect

Les modes indirects sont utiles pour le traitement des tableaux et autres boucles. Avec le mode 5/6 cycle “(indirect), y”, le registre Y 8 bits est ajouté à une adresse de base 16 bits lue à partir de la page zéro, qui est localisée par un seul octet après l’opcode. Le registre Y est donc un registre d’ index dans le sens où il est utilisé pour contenir un index réel(par opposition au registre X du 6800, où une adresse de base était directement stockée et à laquelle un décalage immédiat pouvait être ajouté). L’incrémentation du registre d’index pour parcourir le tableau octet par octet ne prend que deux cycles supplémentaires. Avec le mode “(indirect,x)” moins fréquemment utilisé, l’adresse effective de l’opération se trouve à l’adresse de page zéro formée en ajoutant le deuxième octet de l’instruction au contenu du registre X. En utilisant les modes indexés, la page zéro agit effectivement comme un ensemble de jusqu’à 128 registres d’adresses supplémentaires (bien que très lents).

Le 6502 est capable d’effectuer des additions et des soustractions en binaire ou en décimal codé binaire . Placer le processeur en mode BCD avec l’ SEDinstruction (set D flag) entraîne une arithmétique décimale, ce $99 + $01qui entraînerait $00 et le drapeau de report (C) étant défini. En mode binaire ( CLD, effacer l’indicateur D), la même opération entraînerait $9A et l’indicateur de retenue serait effacé. À part Atari BASIC , le mode BCD était rarement utilisé dans les applications domestiques.

Voir le Hello world ! article pour un exemple simple mais caractéristique du langage d’assemblage 6502 .

Instructions et opcodes

Les codes d’opération d’instruction 6502 ( opcodes ) ont une longueur de 8 bits et ont la forme générale AAABBBCC, où AAA et CC définissent l’opcode et BBB définit le mode d’adressage. [73]

Par exemple, considérons l’ ORAinstruction, qui effectue un OU au niveau du bit sur les bits de l’accumulateur avec une autre valeur. L’opcode d’instruction est de la forme 000bbb01, où bbb peut être 010 pour une valeur de mode immédiat (constante), 001 pour une adresse fixe de page zéro, 011 pour une adresse absolue, etc. [73]

Ce schéma n’est pas absolu et il existe un certain nombre d’exceptions. Cependant, là où cela s’applique, cela permet de déconstruire facilement les valeurs d’opcode en mnémoniques d’assemblage pour la majorité des instructions, en gérant les cas extrêmes avec du code à usage spécial. [73]

Sur les 256 opcodes possibles disponibles en utilisant un modèle de 8 bits, le 6502 d’origine en utilise 151, organisés en 56 instructions avec (éventuellement) plusieurs modes d’adressage . Selon l’instruction et le mode d’adressage, l’opcode peut nécessiter zéro, un ou deux octets supplémentaires pour les opérandes. Par conséquent, les instructions machine 6502 varient en longueur de un à trois octets. [74] [75] L’opérande est stocké dans le format little-endian habituel du 6502 .

Le 65C816 , le descendant CMOS 16 bits du 6502, prend également en charge l’adressage 24 bits, ce qui entraîne l’assemblage d’instructions avec des opérandes à trois octets, également disposés au format petit-boutiste.

Les 105 opcodes restants ne sont pas définis. Dans la conception originale, les instructions où les 4 bits de poids faible ( quartet ) étaient 3, 7, B ou F n’étaient pas utilisées, laissant de la place pour une expansion future. De même, la colonne $2x n’avait qu’une seule entrée, . Les 25 emplacements vides restants ont été distribués. Certains des emplacements vides ont été utilisés dans le 65C02 pour fournir à la fois de nouvelles instructions et des variations sur celles existantes avec de nouveaux modes d’adressage. Les instructions $Fx ont été initialement laissées libres pour permettre aux fournisseurs tiers d’ajouter leurs propres instructions, mais les versions ultérieures du 65C02 ont normalisé un ensemble d’instructions de manipulation de bits développées par Rockwell Semiconductor .LDX #constant

Langage d’assemblage

Une instruction en langage assembleur 6502 se compose d’un mnémonique d’instruction à trois caractères , suivi de n’importe quel opérande . Les instructions qui ne prennent pas d’opérande séparé mais ciblent un seul registre basé sur le mode d’adressage combinent le registre cible dans le mnémonique de l’instruction, de sorte que l’assembleur utilise INXplutôt que INC Xpour incrémenter le registre X.

Tableau d’instructions

| Matrice d’opcode pour le jeu d’instructions 6502 | ||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Modes d’adressage : A – accumulateur, # – immédiat, zpg – page zéro, abs – absolu, ind – indirect, X – indexé par le registre X, Y – indexé par le registre Y, rel – relatif | ||||||||||||

| Grignotage élevé | Faible grignotage | |||||||||||

| 0 | 1 | 2 | 4 | 5 | 6 | 8 | 9 | UN | C | ré | E | |

| 0 | BRK | ORA ( ind ,X) | ORA _ | zpg ASL | PHP | ORA # | LSA A | ORA abdominaux | ASL abdominaux | |||

| 1 | BPL relatif | ORA ( ind ),Y | ORA zpg ,X | ASL zpg ,X | CLC | ORA abs ,Y | ORA abs ,X | ASL abdos ,X | ||||

| 2 | JSR abs | ET ( ind ,X) | BIT zpg | ET zpg | ROLzpg _ | PLP | ET # | ROLE A | BIT abs | ET abs | ROL abs | |

| 3 | IMC relatif | ET ( ind ),Y | ET zpg ,X | ROLzpg , X | SECONDE | ET abs ,O | ET abs ,X | ROL abs ,X | ||||

| 4 | RTI | EOR ( ind ,X) | EOR zpg | LSR zpg | PHA | N° EOR | RLS A | ABS JMP | EOR abs | Abs LSR | ||

| 5 | BVC rel | EOR ( ind ),Y | EOR zpg ,X | LSR zpg ,X | CLI | EOR abs ,Y | EOR abs ,X | LSR abs ,X | ||||

| 6 | RTS | ADC ( ind ,X) | ADC zpg | RDR zpg | PLA | N° ADC | ROR A | JMP ( ind ) | ADC abs | RDR abs | ||

| 7 | BVS rel | ADC ( ind ),Y | CAN zpg ,X | ROR zpg ,X | SEI | ADC abs ,Y | ADC abs , X | RDR abs ,X | ||||

| 8 | STA ( ind ,X) | STY zpg | STA zpg | STX zpg | DEY | ATX | abdominaux STY | ABS ABS | ABS STX | |||

| 9 | BCC rel | STA ( ind ),Y | STY zpg ,X | STA zpg ,X | STX zpg ,Y | TYA | STA abs ,Y | TXS | ABS ABS ,X | |||

| UN | LDY # | LDA ( ind ,X) | N° LDX | LDYzpg _ | LDAzpg _ | LDX zp | TAÏ | N° ADL | IMPÔT | ABS LDY | LDA abs | Abdos LDX |

| B | BCS rel | LDA ( ind ),Y | LDY zpg ,X | LDAzpg , X | LDX zpg , O | CLV | Abs LDA , O | TSX | LDY abs ,X | Abs LDA , X | Abs LDX , Y | |

| C | # CPJ | CMP ( ind ,X) | CPY zpg | CMPzpg _ | DEC zpg | INY | CMP # | DEX | CPY abs | CMP abs | DEC abs | |

| ré | BNE rel | CMP ( ind ),Y | CMP zpg ,X | DEC zpg ,X | CLD | CMP abs ,Y | CMP abs ,X | DEC abs ,X | ||||

| E | N° CPX | SBC ( ind ,X) | CPXzpg _ | SBC zpg | INC zpg | INX | # CCS | NON | ABS CPX | SBC abs | INC abs | |

| F | BEQ relatif | SBC ( ind ),Y | SBC zpg ,X | INC zpg ,X | SED | SBC abs ,Y | Abs SBC ,X | INC abs ,X | ||||

| Les opcodes vides (par exemple, F2 ) et tous les opcodes dont les quartets bas sont 3 , 7 , B et F ne sont pas définis dans le jeu d’instructions 6502. |

Comportement détaillé

Matrice de processeur 6502 avec transistors NMOS dessinés et étiquettes faisant allusion à la fonctionnalité des composants du 6502

Matrice de processeur 6502 avec transistors NMOS dessinés et étiquettes faisant allusion à la fonctionnalité des composants du 6502

L’entrée d’ interruption non masquable (NMI) du processeur est sensible aux fronts , ce qui signifie que l’interruption est déclenchée par le front descendant du signal plutôt que par son niveau. L’implication de cette fonctionnalité est qu’un circuit d’interruption OU câblé n’est pas facilement pris en charge. Cependant, cela empêche également les interruptions NMI imbriquées de se produire jusqu’à ce que le matériel rende à nouveau l’entrée NMI inactive, souvent sous le contrôle du gestionnaire d’interruptions NMI .

L’assertion simultanée des lignes d’interruption matérielle NMI et IRQ (masquable) entraîne l’ignorance de l’IRQ. Cependant, si la ligne IRQ reste affirmée après le service de la NMI, le processeur répondra immédiatement à l’IRQ, car l’IRQ est sensible au niveau . Ainsi, une sorte de priorité d’interruption intégrée a été établie dans la conception 6502.

Le drapeau B est défini par le 6502 échantillonnant périodiquement la sortie de son détecteur de front NMI et son entrée IRQ. Le signal IRQ entraîné à l’état bas n’est cependant reconnu que si les IRQ sont autorisées par le drapeau I. Si de cette manière une demande NMI ou une IRQ (masquable) est détectée, le drapeau B est mis à zéro et amène le processeur à exécuter ensuite l’instruction BRK au lieu d’exécuter l’instruction suivante basée sur le compteur de programme. [76] [77]

L’instruction BRK pousse alors l’état du processeur sur la pile, avec le bit d’indicateur B mis à zéro. A la fin de son exécution, l’instruction BRK remet à un la valeur du drapeau B. C’est la seule façon de modifier le drapeau B. Si une instruction autre que l’instruction BRK pousse le drapeau B sur la pile dans le cadre de l’état du processeur [78] , le drapeau B a toujours la valeur un.

Une transition de haut en bas sur la broche d’entrée SO définira le bit d’état de débordement du processeur. Cela peut être utilisé pour une réponse rapide au matériel externe. Par exemple, un pilote de périphérique d’ interrogation à grande vitesse peut interroger le matériel une fois en seulement trois cycles à l’aide d’une BVCinstruction Branch-on-oVerflow-Clear ( ) qui se branche sur elle-même jusqu’à ce que le débordement soit défini par une transition descendante SO. Le Commodore 1541 et d’autres lecteurs de disquettes Commodore utilisent cette technique pour détecter le moment où le sérialiseur est prêt à transférer un autre octet de données sur le Disque. La conception matérielle et logicielle du système doit garantir qu’un SO ne se produira pas pendant le traitement arithmétique et ne perturbera pas les calculs.

Variations et dérivés

Il existait de nombreuses variantes du NMOS 6502 d’origine.

| Société | Modèle | La description |

|---|---|---|

| 6502A | Une puce de 1,5 MHz utilisée dans Asteroids Deluxe . | |

| 6502B | Version du 6502 capable de fonctionner à une vitesse maximale de 2 MHz au lieu de 1. Le B était utilisé dans l ‘ Apple III , le BBC Micro et, cadencé à 1,79 MHz, les premiers ordinateurs Atari 8 bits . | |

| 6502C | Le 6502C “officiel” était une version du 6502 original capable de fonctionner jusqu’à 4 MHz.

À ne pas confondre avec SALLY, un 6502 personnalisé conçu pour Atari (et parfois appelé par eux “6502C” [79] ) ni avec le 65C02 du même nom . |

|

| SALLY / C014806 / “6502C” | Variante 6502 personnalisée conçue pour Atari, utilisée dans les ordinateurs Atari 8 bits ultérieurs ainsi que dans les consoles Atari 5200 et Atari 7800 .

Possède un signal HALT sur la broche 35 et le signal R/W sur la broche 36 (ces broches ne sont pas connectées (N/C) sur un 6502 standard). Tirer HALT vers le bas verrouille l’horloge, mettant le processeur en pause. Cela a été utilisé pour permettre l’accès direct à la mémoire (DMA) du circuit vidéo. [80] Bien que parfois appelé “6502C” dans la documentation Atari, ce n’est pas la même chose que le 6502C “officiel” et la puce elle-même n’est jamais marquée comme telle. [79] |

|

| MOS | 6503 | Capacité d’adressage mémoire réduite (4 Ko) et pas d’entrée RDY, dans un boîtier DIP à 28 broches (avec les broches phase 1 (OUT), SYNC, Vss redondantes et SO du 6502 également omises). [81] |

| MOS | 6504 | Capacité d’adressage mémoire réduite (8 Ko), pas d’entrée NMI et pas d’entrée RDY, dans un boîtier DIP à 28 broches (avec les broches phase 1 (OUT), SYNC, Vss redondantes et SO du 6502 également omises). [81] |

| MOS | 6505 | Capacité d’adressage mémoire réduite (4 Ko) et pas de NMI, dans un boîtier DIP à 28 broches (avec les broches phase 1 (OUT), SYNC, Vss redondantes et SO du 6502 également omises). [81] |

| MOS | 6506 | Capacité d’adressage mémoire réduite (4 Ko), pas d’entrée NMI et pas d’entrée RDY, mais les 3 broches d’horloge du 6502 (c’est-à-dire une horloge de sortie à 2 phases), dans un boîtier DIP à 28 broches (avec le SYNC, Vss redondant, et broches SO du 6502 également omises). [81] |

| MOS | 6507 | Capacité d’adressage mémoire réduite (8 Ko) et aucune interruption, dans un boîtier DIP à 28 broches (avec les broches phase 1 (OUT), SYNC, Vss redondantes et SO du 6502 également omises). [81] Cette puce a été utilisée dans le système de jeu vidéo Atari 2600 . |

| MOS | 6508 | Possède un port d’entrée/sortie 8 bits intégré et 256 octets de RAM statique interne. |

| MOS | 6509 | Peut adresser jusqu’à 1 Mo de RAM en 16 banques de 64 Ko et a été utilisé dans la série Commodore CBM-II . |

| MOS | 6510 | Possède un port d’entrée/sortie programmable 6 bits intégré et a été utilisé dans le Commodore 64 . Le 8500 est en fait une version HMOS du 6510 et l’a remplacé dans les versions ultérieures du C64. |

| MOS | 6512 6513 6514 6515 |

La technologie MOS 6512, 6513, 6514 et 6515 reposent chacune sur une horloge externe, au lieu d’utiliser un générateur d’horloge interne comme le 650x (par exemple 6502). Cela a été utilisé avec avantage dans certaines conceptions où les horloges pouvaient être exécutées de manière asymétrique, augmentant les performances globales du processeur.

Le 6512 est un 6502 avec une entrée d’horloge à 2 phases pour un oscillateur d’horloge externe, au lieu d’un oscillateur d’horloge intégré. [81] Les 6513, 6514 et 6515 sont également équivalents à (respectivement) un 6503, 6504 et 6505 avec la même entrée d’horloge à 2 phases. [81] Le 6512 a été utilisé dans le BBC Micro B+64 . |

| Ricoh | 2A03 | Variante 6502 comprenant une unité de traitement audio et dépourvue du mode BCD, utilisée dans le Nintendo Entertainment System . |

| MOS | 6591 6592 |

Conceptions de Système sur puce qui utilisent un Atari 2600 complet dans un boîtier DIP à 48 broches. [82] [83] |

| WDC | 65C02 | Version CMOS du NMOS 6502 conçue par Bill Mensch du Western Design Center (WDC), avec une consommation d’énergie réduite, la prise en charge de vitesses d’horloge beaucoup plus élevées, de nouvelles instructions, de nouveaux modes d’adressage pour certaines instructions existantes et la correction des errata NMOS, comme le JMP ($xxFF)bogue. |

| WDC | 65SC02 | Variante du WDC 65C02 sans opérations de manipulation de bits individuelles (RMB, SMB, BBR et BBS). [84] Ce noyau, fonctionnant à 4 MHz, était utilisé dans le circuit intégré principal du système Atari Lynx . |

| CSG / MOS | 65CE02 | Dérivé CMOS développé par le Commodore Semiconductor Group (CSG), anciennement MOS Technology. |

| Rockwell | R6511Q R6500/11, R6500/12, R6500/15 ” Micro-ordinateurs monopuce “ |

Versions améliorées du processeur basé sur 6502, comprenant également des opérations de manipulation de bits individuels (RMB, SMB, BBR et BBS), une RAM de 192 octets à page zéro sur puce, UART , etc. [85] [86] |

| Rockwell | R65F11 R65F12 |

Le Rockwell R65F11 (introduit en 1983) et le R65F12 ultérieur sont des versions améliorées du processeur basé sur 6502, comprenant également des opérations de manipulation de bits individuelles (RMB, SMB, BBR et BBS), une RAM à page zéro sur puce, une puce Forth noyau ROM, un UART, etc. [87] [88] [89] [90] [91] |

| GTE | G65SC102 | Logiciel compatible avec le 65C02, mais avec un circuit de brochage et d’oscillateur légèrement différent. Le BBC Master Turbo incluait la version 4 MHz de ce CPU sur une carte coprocesseur, qui pouvait également être achetée séparément et ajoutée au Master 128. |

| Rockwell | R65C00 R65C21 R65C29 |

Les R65C00, R65C21 et R65C29 ont deux CMOS 6502 améliorés dans une seule puce, et les R65C00 et R65C21 contenaient en outre 2 Ko de ROM programmable par masque. [92] [93] |

| CM630 | Un clone Eastern Bloc 1 MHz du 6502 et a été utilisé dans les Pravetz 8A et 8C, clones bulgares de la série Apple // . [94] | |

| MOS | 7501 8501 |

Variantes du 6510 (lui-même un 6502 amélioré), introduit en 1984. [95] Ils ont étendu le nombre de broches de port d’E / S de 6 à 7, mais ont omis les broches pour les interruptions non masquables et la sortie d’horloge. [96] Utilisé dans les ordinateurs C-16 , C-116 et Plus/4 de Commodore . La principale différence entre les processeurs 7501 et 8501 est que le 7501 a été fabriqué avec le processus HMOS-1 et le 8501 avec HMOS-2. [95] |

| MOS | 8500 | Introduit en 1985 en tant que version HMOS du 6510 (qui est à son tour basé sur le 6502). Hormis la modification du processus, le 8500 est pratiquement identique à la version NMOS du 6510. Il a remplacé le 6510 dans les versions ultérieures du Commodore 64 . |

| MOS | 8502 | Conçu par MOS Technology et utilisé dans le Commodore 128 . Basé sur le MOS 6510 utilisé dans le Commodore 64, le 8502 pouvait fonctionner à une fréquence d’horloge double du 6510. [97] La famille 8502 comprend également les MOS 7501, 8500 et 8501. |

| Hudson doux | HuC6280 | Version améliorée du WDC 65C02 de la société japonaise de jeux vidéo Hudson Soft . Fabriqué pour eux par Seiko Epson et NEC pour le SuperGrafx . Le produit le plus notable utilisant le HuC6280 est la console de jeux vidéo TurboGrafx-16 de NEC. |

Dérivés 16 bits

Le Western Design Center a conçu et produit actuellement le processeur W65C816S , un successeur 16 bits à cœur statique du 65C02 . Le W65C816S est une variante plus récente du 65C816, qui est le cœur de l’ ordinateur Apple II GS et la base du processeur Ricoh 5A22 qui alimente le système de divertissement Super Nintendo.. Le W65C816S intègre des améliorations mineures par rapport au 65C816 qui font que la nouvelle puce n’est pas un remplacement exact compatible avec le matériel pour la précédente. Parmi ces améliorations figurait la conversion en un cœur statique, qui permet d’arrêter l’horloge dans l’une ou l’autre phase sans que les registres ne perdent de données. Disponible auprès des distributeurs d’électronique, à partir de mars 2020, le W65C816S est officiellement évalué pour un fonctionnement à 14 MHz.

Le Western Design Center a également conçu et produit le 65C802 , qui était un cœur 65C816 avec un espace d’adressage de 64 kilo-octets dans un boîtier compatible avec les broches 65 (C) 02. Le 65C802 pourrait être adapté à une carte 6502 et fonctionnerait comme un 65C02 à la mise sous tension, fonctionnant en “mode émulation”. Comme avec le 65C816, une séquence de deux instructions ferait passer le 65C802 en fonctionnement “mode natif”, exposant son accumulateur 16 bits et ses Registres d’index , ainsi que d’autres fonctionnalités du 65C816. Le 65C802 n’a pas été largement utilisé et la production a été interrompue.

Exemple de code

Le code source du langage d’assemblage 6502 suivant est destiné à une sous-routine nommée , qui copie une chaîne de caractères terminée par un caractère nul d’un emplacement à un autre, en convertissant les caractères majuscules en lettres minuscules. La chaîne copiée est la “source”, et la chaîne dans laquelle la source convertie est stockée est la “destination”.TOLOWER

| 0080 0080 00 04 0082 00 05 0600 0600 A0 00 0602 B1 80 0604 F0 11 0606 C9 41 0608 90 06 060 A C9 5 B 060 C B0 02 060 E 09 20 0610 91 82 0612 C8 0613 D0 ED 0615 38 0616 60 0617 91 82 0619 18 061 A 60 061B _ | ; TOLOWER : ; ; Convertit une chaîne de caractères terminée par un caractère nul en minuscules. ; La longueur maximale de la chaîne est de 255 caractères, plus le terme nul- ; inateur. ; ; Paramètres : ; ; SRC{{snd}} Adresse de la chaîne source ; DST{{snd}} Adresse de chaîne de destination ; ORG 0080 $ ; SRC .WORD $0400 ;pointeur de chaîne source DST .WORD $0500 ;pointeur de chaîne destination ; ORG $0600 ;adresse de début d’exécution ; TOLOWER LDY # $00 ;index de départ ; LOOP LDA ( SRC ), Y ; obtenir de la chaîne source BEQ DONE ; fin de chaîne ; CMP # ‘A’ ;si inférieur à l’alphabet UC… BCC SKIP ;copie inchangée ; CMP # ‘Z’ + 1 ;si supérieur à l’alphabet UC… BCS SKIP ;copie inchangée ; ORA # %00100000 ; convertir en minuscules ; SKIP STA ( DST ), Y ;stocker dans la chaîne de destination INY ; index de saut BOUCLE BNE ;caractère suivant ; ; REMARQUE : si Y est renvoyé à la ligne, la chaîne de destination sera laissée dans un ; Etat. Nous définissons carry pour l’indiquer à la fonction appelante. ; SEC ;rapporter une erreur de chaîne trop longue &… RTS ;retourner à l’appelant ; DONE STA ( DST ), Y ;terminer la chaîne de destination CLC ;convertir le rapport terminé &… RTS ;retourner à l’appelant ; .FINIR |

Bugs et bizarreries

Le 6502 présentait plusieurs bogues et bizarreries, dont il fallait tenir compte lors de sa programmation :

- Les premières révisions du 6502, telles que celles livrées avec certains ordinateurs KIM-1 , avaient un bogue grave dans l’ instruction ROR (rotation de la mémoire ou de l’accumulateur à droite). Le fonctionnement de ROR dans ces puces est en fait une instruction ASL (décalage arithmétique à gauche) qui n’affecte pas le bit de retenue dans le registre d’état. MOS a laissé l’instruction hors de la documentation de la puce entièrement à cause du défaut, promettant que ROR apparaîtrait sur les puces 6502 à partir de 1976. [98] La grande majorité des puces 6502 existantes aujourd’hui ne présentent pas ce bogue.

- La famille NMOS 6502 possède une variété d’ instructions non documentées , qui varient d’un fabricant de puces à l’autre. Le décodage de l’instruction 6502 est implémenté dans un réseau logique câblé (similaire à un réseau logique programmable ) qui n’est défini que pour 151 des 256 opcodes disponibles . Les 105 autres déclenchent des actions étranges et parfois difficiles à prévoir, telles que planter le processeur, exécuter deux instructions valides consécutivement, effectuer d’étranges mélanges de deux instructions ou simplement ne rien faire du tout. Eastern House Software a développé le “Trap65”, un appareil qui se branche entre le processeur et son socket pour convertir (piéger) les opcodes non implémentés en BRK(interruption logicielle). [ citation nécessaire ] Certains programmeurs ont utilisé cette fonctionnalité pour étendre le jeu d’instructions 6502 en fournissant des fonctionnalités pour les opcodes non implémentés avec un logiciel spécialement écrit intercepté au vecteur 0xFFFE de l’instruction BRK. [99] [100] Tous les opcodes indéfinis ont été remplacés par des instructions NOP dans le 65C02 , une version CMOS améliorée du 6502, bien qu’avec des tailles d’octets et des temps d’exécution variables. Dans le 65C802/65C816 , les 256 opcodes effectuent des opérations définies.

- L’ instruction de saut indirect de la mémoire du 6502 , JMP (<address>), est partiellement interrompue. Si <adresse> est hexadécimal xxFF (c’est-à-dire, tout mot se terminant par FF ), le processeur ne sautera pas à l’adresse stockée dans xxFF et xxFF+1comme prévu, mais plutôt à celle définie par xxFF et xx00 (par exemple, JMP ($10FF)sauterait à l’adresse stocké dans 10FF et 1000, au lieu de celui stocké dans 10FF et 1100). Ce défaut s’est poursuivi sur toute la gamme NMOS, mais a été corrigé dans les dérivés CMOS.

- L’adressage indexé NMOS 6502 au-delà des limites de page effectuera une lecture supplémentaire d’une adresse invalide. Cette caractéristique peut causer des problèmes aléatoires en accédant au matériel qui agit sur une lecture, comme l’effacement du temporisateur ou des indicateurs IRQ, l’envoi d’une poignée de main d’E/S, etc. Ce défaut s’est poursuivi sur toute la ligne NMOS, mais a été corrigé dans les dérivés CMOS, en lequel le processeur effectue une lecture supplémentaire du dernier octet d’instruction.

- Les instructions de lecture-modification-écriture du 6502 effectuent un cycle de lecture et deux cycles d’écriture. Tout d’abord, les données non modifiées qui ont été lues sont réécrites, puis les données modifiées sont écrites. Cette caractéristique peut entraîner des problèmes en accédant deux fois au matériel qui agit sur une écriture. Cette anomalie s’est poursuivie sur toute la ligne NMOS, mais a été corrigée dans les dérivés CMOS, dans lesquels le processeur effectuera deux lectures et un cycle d’écriture. La pratique de la programmation défensive évitera généralement ce problème en n’exécutant pas les instructions de lecture/modification/écriture sur les registres matériels.

- Les drapeaux d’état N (résultat négatif), V (débordement de bit de signe) et Z (résultat zéro) sont généralement sans signification lors de l’exécution d’opérations arithmétiques alors que le processeur est en mode BCD , car ces drapeaux reflètent le résultat binaire, et non BCD. Cette limitation a été supprimée dans les dérivés CMOS. Par conséquent, cette fonctionnalité peut être utilisée pour distinguer un processeur CMOS d’une version NMOS. [101]

- Si le 6502 se trouve en mode BCD lorsqu’une interruption matérielle se produit, il ne reviendra pas en mode binaire. Cette caractéristique peut entraîner des bogues obscurs dans la routine de service d’interruption si elle ne parvient pas à effacer le mode BCD avant d’effectuer des opérations arithmétiques. Par exemple, le KERNAL du Commodore 64 ne gérait pas correctement cette caractéristique du processeur, nécessitant que les IRQ soient désactivées ou re-vectorisées pendant les opérations mathématiques BCD. Ce problème a également été résolu dans les dérivés CMOS.

- Le jeu d’instructions 6502 comprend BRK (opcode $ 00), qui est techniquement une interruption logicielle (similaire dans l’esprit au mnémonique SWI des processeurs Motorola 6800 et ARM ). BRK est le plus souvent utilisé pour interrompre l’exécution du programme et démarrer un moniteur de langage machine pour tester et déboguer pendant le développement du logiciel. BRK pourrait également être utilisé pour acheminer l’exécution du programme à l’aide d’une simple table de sauts (analogue à la manière dont l’ Intel 8086 et ses dérivés gèrent les interruptions logicielles par numéro). Cependant, si une interruption matériellese produit lorsque le processeur récupère une instruction BRK, la version NMOS du processeur ne parviendra pas à exécuter BRK et procédera à la place comme si seule une interruption matérielle s’était produite. Ce défaut a été corrigé dans l’implémentation CMOS du processeur.

- Lors de l’exécution des instructions JSR (saut au sous-programme) et RTS (retour du sous-programme), l’adresse de retour poussée vers la pile par JSR est celle du dernier octet de l’opérande JSR (c’est-à-dire l’octet le plus significatif de l’adresse du sous-programme), plutôt que l’adresse de l’instruction suivante. En effet, la copie proprement dite (du compteur de programme vers la pile puis inversement) a lieu avant l’incrémentation automatique du compteur de programme qui se produit à la fin de chaque instruction. [102] Cette caractéristique passerait inaperçue à moins que le code n’examine l’adresse de retour afin de récupérer les paramètres dans le flux de code (un idiome de programmation 6502 documenté dans le ProDOS 8 Technical Reference Manual). Il reste une caractéristique de 6502 dérivés à ce jour.

Voir également

- Liste des 6502 assembleurs

- Ordinateurs personnels basés sur la technologie MOS 6502

- Interruptions dans les processeurs 65xx

- Nombre de transistors

- Accélérateurs Apple II

- cc65 – Assembleur de macros 6502 et compilateur C

Remarques

- ^ À cette époque, la littérature technique indiquait la longueur et la largeur de chaque puce en “mils” (0,001 pouce).

- ^ Un exemple d’une telle conception était la famille d’ordinateurs personnels Atari 8 bits , qui utilisait DMA pour partager la mémoire entre le 6502 et la puce vidéo ANTIC. Cela a été implémenté avec une seule bascule, qui a ensuite été intégrée dans les versions personnalisées “Sally” du 6502 utilisé dans ces machines. [45]

Références

Citations

- ^ “Le MOS 6502 et le meilleur gars de mise en page au monde” . swtch.com. 2011-01-03 . Récupéré le 09/08/2014 .

- ^ “MONSter6502” . monster6502.com. 2017 . Récupéré le 01/05/2017 .

- ^ William Mensch, Rob Walker (9 octobre 1995). Entretien avec William Mensch (vidéo Web). Atherton, Californie : Silicon Genesis, bibliothèques de l’Université de Stanford. Archivé de l’original le 14 mai 2012 . Consulté le 4 juin 2012 . William Mensch et le modérateur prononcent tous deux le microprocesseur 6502 comme “soixante-cinq-oh-deux” .

- ^ “Centre de conception occidental (WDC) Accueil de la technologie de microprocesseur 65xx” . www.westerndesigncenter.com . Récupéré le 08/04/2019 .

- ^ “Motorola poursuit la technologie MOS” (PDF) . Recueil de micro-ordinateurs . Cupertino CA : Microcomputer Associates. 2 (6): 11. Décembre 1975. [ lien mort permanent ]

- ^ “Motorola rejoint la course des microprocesseurs avec une entrée 8 bits” . Électronique . New York : McGraw Hill. 47 (5) : 29-30. 7 mars 1974.

- ^ Histoire orale de Motorola 6800 (2008), p. 9

- ^ Buchanan, John K., “Circuit amplificateur de tension MOS DC”, brevet américain 3942047 , délivré le 2 mars 1976.

- ^ Buchanan, John K., “Chip topography for MOS integrated circuitry microprocessor chip”, brevet américain 3987418 , délivré le 19 octobre 1976.

- ^ Histoire orale de Motorola 6800 (2008), p. 8

- ^ Mensch Oral History (1995) Mensch a obtenu un diplôme d’associé de l’Université Temple en 1966, puis a travaillé chez Philco Ford en tant que technicien en électronique avant de fréquenter l’Université de l’Arizona.

- ^ Mensch, William D., “Chip topography for MOS interface circuit”, brevet américain 3968478 , délivré le 6 juillet 1976.

- ^ Jenkins, François; Lane, E.; Lattin, W.; Richardson, W. (novembre 1973). “Modélisation de dispositifs MOS pour la mise en œuvre informatique”. Transactions IEEE sur la théorie des circuits . IEEE. 20 (6): 649–658. doi : 10.1109/tct.1973.1083758 . ISSN 0018-9324 . Tous les auteurs appartenaient à la division des produits semi-conducteurs de Motorola.

- ^ Donohue, James F. (27 octobre 1988). “Le microprocesseur deux premières décennies: la façon dont c’était”. EDN . Éditions Cahners. 33 (22A) : 18–32. ISSN 0012-7515 . Page 30. Bennett travaillait déjà sur ce qui est devenu le 6800. “Il m’a embauché,” dit Peddle à propos de Bennett, “pour faire le travail de support architectural pour le produit qu’il avait déjà commencé.” … dit Peddle. “Motorola a essayé de le tuer plusieurs fois. Sans Bennett, le 6800 n’aurait pas eu lieu, et une grande partie de l’industrie n’aurait pas eu lieu non plus.”

- ^ Hepworth, Edward C., Rodney J. Means, Charles I. Peddle, “Adaptateur d’interface de communication asynchrone”, brevet 3975712 , délivré le 17 août 1976. Remarque : Motorola classe généralement les inventeurs par ordre alphabétique.

- ^ Motorola (5 août 1976). “Ils restent devant avec la famille M6800 de Motorola” . Électronique . McGraw-Hill. 49 (16): 51. Publicité montrant trois applications embarquées de TRW, HP et RUSCO.

- ^ Histoire orale de Motorola 6800 (2008), p. 89

- ^ “C’est toute la famille de produits” . Électronique . New York : McGraw Hill. 48 (1): 37. 9 janvier 1975. Publicité Motorola mettant l’accent sur leur ensemble complet de puces périphériques et d’outils de développement. Cela raccourcit le cycle de conception des produits des clients.

- ^ Histoire orale de Motorola 6800 (2008) p. 18

- ^ “L’ensemble de microprocesseurs Motorola est de 1 MHz n-MOS” . Ingénierie de contrôle . 21 (11): 11. Novembre 1974. Le prix du microprocesseur MC6800 était de 360 $. L’adaptateur d’interface de communication asynchrone MC6850 (ACIA) devait être introduit au premier trimestre 1975.

- ^ Intel Corporation (1984). Kaye, Glynnis Thompson (éd.). Une révolution en cours – Une histoire à ce jour d’Intel (PDF) . Société intel. p. 14. Numéro de commande : 231295. Archivé (PDF) de l’original le 23 octobre 2012 . Récupéré le 30 décembre 2016 . “Shima a implémenté le 8080 en environ un an et le nouvel appareil a été introduit en avril 1974 pour 360 $.”

- ^ “Motorola monte le lecteur M6800” . Électronique . New York : McGraw Hill. 48 (8): 25. 17 avril 1975. “Les distributeurs sont en stock avec la famille M6800, et la division propose également un kit d’introduction qui comprend les six pièces initiales de la famille, ainsi que des applications et des manuels de programmation, pour 300 $.”

- ^ Entretien 2014 , 52:30.

- ^ Entretien 2014 , 54:45.

- ^ Bagnal (2010), p. 11. La nouvelle offre de Peddle est arrivée à un moment opportun pour les 6800 développeurs. “Ils ne voulaient pas aller à Austin, au Texas”, explique Mensch.

- ^ Entretien 2014 , 54:40.

- ^ Entretien 2014 , 55:50.

- ^ Waller, Larry (13 novembre 1975). “Motorola cherche à mettre fin au dérapage”. Électronique . New York : McGraw Hill. 48 (23): 96–98. Résumé : Produits semi-conducteurs divisés en deux parties, les circuits intégrés et les composants discrets. Les pertes de semi-conducteurs pour les quatre derniers trimestres ont dépassé 30 millions de dollars. L’organisation commerciale a perdu sa sensibilité aux besoins des clients, “les retards dans la réponse aux baisses de prix ont fait que les clients ont acheté ailleurs”. Des problèmes techniques ont tourmenté la production de circuits intégrés. Les problèmes ne sont “pas dans la conception, mais dans les rendements des puces et des matrices”. Les problèmes ont été résolus. Le microprocesseur MC6800 “est arrivé en novembre 1974”.

- ^ Entretien 2014 , 56:30.

- ^ Entretien 2014 , 55:00.

- ^ Bagnal (2010), p. 13.

- ^ Technologie MOS (14 novembre 1974). “Les premières matrices de calculatrices scientifiques à puce unique” . Électronique . McGraw-Hill. 47 (23): 90–91.

- ^ Entretien 2014 , 57:00.

- ^ Entretien 2014 , 58:30.

- ^ Cass, Stephen (16 septembre 2021). “Q&A avec le co-créateur du processeur 6502” . Spectre IEEE .

- ^ Ho, Joshua (9 octobre 2014). “Une introduction à la physique, à la technologie et à l’industrie des semi-conducteurs” . Anandtech .

- ^ Histoire orale de Motorola 6800 (2008), p. dix.

- ^ un bc Cushman 1975 , p. 40.

- ^ “Microprocesseur 8080A – boîtier DIP 40” . Monde CPU .

- ^ un b Cushman 1975 , p. 38.

- ^ un b “les Jalons de Loi de Moore” . IEEE .

- ^ Bagnal (2010), p. 19: “Paivinen a promis à Peddle qu’il aurait le processus de canal n prêt. Il a été fidèle à sa parole.”

- ^ un bc Cushman 1975 , p. 36.

- ^ un bc Cushman 1975 , p. 41.

- ^ Purcaru, John (2014). Jeux contre matériel. L’histoire des jeux vidéo sur PC : les années 80 . p. 317.

- ^ Entretien 2014 , 1:01:00.

- ^ Entretien 2014 , 1:02:00.

- ^ Entretien 2014 , 1:02:30.

- ^ La fiche technique d’août 1975 contenait 55 instructions sans ROR, la fiche technique de mai 1976 contenait le ROR et 56 instructions. Fichier:Ensemble d’instructions MCS650x.jpg

- ^ Université de Stanford, projet Silicon Genesis: entretien d’histoire orale enregistré sur vidéo de Willam Mensch

- ^ “La gamme de microprocesseurs propose 4, 8, 16 bits” . Électronique . New York : McGraw Hill. 48 (15): 118. 24 juillet 1975. L’article couvre les versions 6501 et 6502 ainsi que les versions à 28 broches qui ne traiteraient que 4K de mémoire. Il couvrait également les futurs appareils tels que “un design que Peddle appelle un pseudo 16”.

- ^ Sugarman, Robert (25 août 1975). « Le pays a-t-il besoin d’un bon microprocesseur à 20 $ ? » (PDF) . EE fois . Manhasset, New York: CMP Publications: 25. Archivé de l’original (PDF) le 3 février 2007 . Récupéré le 5 février 2008 .

- ^ Fylstra, Daniel (novembre 1975). “Fils de Motorola (ou la puce CPU à 20 $ )”. Octet . Peterborough, NH : édition verte. 1 (3): 56–62. Comparaison des microprocesseurs 6502 et 6800. L’auteur a visité MOS Technology en août 1975.

- ^ “Microprocesseur de 3e génération” (PDF) . Recueil de micro-ordinateurs . Cupertino, CA : Associés de micro -ordinateur . 2 (2): 1–3. Août 1975. Archivé de l’original (PDF) le 2009-07-04 . Récupéré le 27/11/2009 .

- ^ “Le microprocesseur MOS 6501 les bat tous” . Électronique . New York : McGraw Hill. 48 (16): 60–61. 7 août 1975.

- ^ “MOS 6502 le deuxième d’une famille de microprocesseurs hautes performances à faible coût” . Ordinateur . Société informatique IEEE. 8 (9) : 38–39. Septembre 1975. doi : 10.1109/CM.1975.219074 .

- ^ Bagnall (2010), p. 33–35.

- ^ Signetics (30 octobre 1975). “Le microprocesseur le plus facile à utiliser” . Électronique . McGraw-Hill. 48 (22): 114–115.

- ^ Motorola (30 octobre 1975). “Tout cela et un microprocesseur dégroupé à 69 $ ” . Électronique . McGraw-Hill. 48 (22): 11. Le prix de la quantité un pour le MC6800 a été réduit de 175 $ à 69 $ . Le prix précédent pour 50 à 99 unités était de 125 $ .

- ^ Waller, Larry (13 novembre 1975). « Nouvelles brèves : Motorola cherche à arrêter l’ennemi du microprocesseur ». Électronique . New York : McGraw Hill. 48 (23): 38. “Motorola a déclaré la semaine dernière qu’il demanderait une injonction immédiate pour empêcher MOS Technology Inc., Norristown, Pennsylvanie, de fabriquer et de vendre des produits à microprocesseur, y compris son MCS6500.” (Ce numéro a été publié le 7 novembre.)

- ^ Motorola was awarded the following US Patents on the 6800 microprocessor family: 3962682, 3968478, 3975712, 3979730, 3979732, 3987418, 4003028, 4004281, 4004283, 4006457, 4010448, 4016546, 4020472, 4030079, 4032896, 4037204, 4040035, 4069510, 4071887, 4086627, 4087855, 4090236, 4145751, 4218740, 4263650.

- ^ Bagnal (2010), p. 53–54. “Il [Mike Janes] avait tout son travail original du 6800 et l’a caché à Motorola…

- ^ “Motorola, MOS Technology règle le procès en matière de brevet” . Électronique . New York : McGraw Hill. 49 (7): 39. 1er avril 1975. “MOS Technology Inc. de Norristown, Pennsylvanie a accepté de retirer son microprocesseur MCS6501 du marché et de payer à Motorola Inc. 200 000 $ …” “MOS Technology et huit anciens employés de Motorola ont rendu, en vertu de documents d’ordonnance du tribunal que Motorola soutient sont confidentiels.” “…les deux sociétés ont convenu d’une licence croisée relative aux brevets dans le domaine des microprocesseurs.”

- ^ Bagnall (2010), p. 55-56

- ^ “Fusions et acquisitions”. Systèmes mini-micro . Cahners. 9 (11): 19. Novembre 1976. ” Commodore International … achète MOS Technology (Norristown, PA). Cela évite à la maison de semi-conducteurs vieille de six ans d’un désastre imminent.”

- ^ un b Goodwins, Rupert (4 décembre 2010). “Les victimes d’Intel : Huit tueurs géants potentiels” . ZDNet . Consulté le 7 mars 2012 . [ lien mort permanent ]

- ^ Reimer, Jérémy. « Part de marché des ordinateurs personnels : 1975-2004 » . Archivé de l’original le 6 juin 2012 . Récupéré le 17/07/2009 .

- ^ “Combien d’ordinateurs Commodore 64 ont été vendus?” . Archivé de l’original le 2016-03-06 . Récupéré le 01/02/2011 .

- ^ “Exécution de code sur un Tamagotchi” . kwartzlab.ca . 7 mai 2013. Archivé de l’original le 2018-08-31 . Récupéré le 23/12/2018 .

- ^ Corder, Mike (printemps 1999). “De grandes choses dans de petits paquets” . Les progrès des pionniers avec la technologie picoJava . Soleil Microélectronique. Archivé de l’original le 12/03/2006 . Consulté le 23 avril 2012 . Le premier 6502 a été fabriqué avec la technologie 8 microns, fonctionnait à un mégahertz et avait une mémoire maximale de 64k.

- ^ “Comment implémenter le partage de bus / DMA sur un système 6502” .

- ^ “MODÈLE DE PROGRAMMATION MCS650X”. MANUEL DE PROGRAMMATION DES MICRO-ORDINATEURS MOS . MOS TECHNOLOGY, INC. Janvier 1976.

- ^ un bc Parker , Neil. “Le jeu d’instructions 6502/65C02/65C816 décodé” . La page Apple II de Neil Parker .

- ^ Jeu d’instructions 6502 .

- ^ Opcodes NMOS 6502 . Archivé le 14/01/2016 à la Wayback Machine .

- ^ “MANIPULATION D’INTERRUPTION” . ogamespec . Récupéré le 15/05/2021 . DRAPEAU B CONTRÔLE ; DRAPEAU B {{cite web}}: CS1 maint: url-status (link)

- ^ “6502 BRK et bit B” . Puces visuelles . Archivé de l’original le 2021-04-05 . Récupéré le 15/05/2021 .

- ^ “DRAPEAUX” . ogamespec . Récupéré le 15/05/2021 . COMBAT; BUS DE DONNÉES INTERNE (DB) {{cite web}}: CS1 maint: url-status (link)

- ^ un b “FAQ 400 800 XL XE : Qu’est-ce que SALLY, ANTIC, CTIA/GTIA/FGTIA, POKEY et FREDDIE ?” . Archivé de l’original le 19 juillet 2020. nommé SALLY par les ingénieurs d’Atari, mais [les documents de support l’appellent] “6502 (modifié)”, “6502 modifié”, “Custom 6502” ou “6502C”. [..] Les puces SALLY 6502 ne sont jamais marquées “6502C” mais, à part l’UMC UM6502I, toujours [marquées] C014806. [..] [Other] puces marquées “6502C” [..] ne sont PAS les Atari “6502C” mais [standard 6502] certifiés pour 4MHz