PCI Express

PCI Express ( Peripheral Component Interconnect Express ), officiellement abrégé en PCIe ou PCI-e , [1] est une norme de Bus d’extension série haute vitesse pour ordinateur , conçue pour remplacer les anciennes normes de bus PCI , PCI-X et AGP . Il s’agit de l’interface de carte mère commune pour les cartes graphiques des ordinateurs personnels , les adaptateurs hôtes de disque dur , les SSD , les connexions matérielles Wi-Fi et Ethernet . [2] PCIe présente de nombreuses améliorations par rapport aux anciennes normes, notamment un Débit de bus système maximal plus élevé , un nombre de broches d’E / S inférieur et une empreinte physique plus petite, une meilleure mise à l’échelle des performances pour les périphériques de bus, un mécanisme de détection et de rapport d’erreurs plus détaillé (Advanced Error Reporting, AER), [3] et fonctionnalité native de remplacement à chaud . Des révisions plus récentes de la norme PCIe fournissent une prise en charge matérielle pour la virtualisation des E/S .

| Interconnexion de composants périphériques Express | |

Logo PCI Express Logo PCI Express |

|

| Année de création | 2003 ; il y a 19 ans ( 2003 ) |

|---|---|

| Créé par |

|

| Remplace |

|

| Largeur en bits | 1 par voie (jusqu’à 16 voies) |

| Nombre d’appareils | 1 sur chaque extrémité de chaque connexion. [un] |

| La vitesse | Double simplex (dans chaque sens) ; exemples en simple voie (×1) et 16 voies (×16) :

|

| Style | En série |

| Interface de branchement à chaud | Oui (avec ExpressCard , OCuLink , CFexpress ou U.2 ) |

| Interface externe | Oui (avec câblage externe OCuLink ou PCI Express ) |

| Site Internet | pcisig.com _ |

Divers emplacements sur une Carte mère d’ordinateur , de haut en bas :

Divers emplacements sur une Carte mère d’ordinateur , de haut en bas :

- PCI express × 4

- PCI express × 16

- PCI express × 1

- PCI express × 16

- PCI conventionnel (32 bits, 5 V)

L’interface électrique PCI Express est mesurée par le nombre de voies simultanées. [4] (Une voie est une seule ligne d’envoi/réception de données. L’analogie est une autoroute avec un trafic dans les deux sens.) L’interface est également utilisée dans une variété d’autres normes, notamment l’ interface de carte d’extension pour ordinateur portable appelée ExpressCard . Il est également utilisé dans les interfaces de stockage de SATA Express , U.2 (SFF-8639) et M.2 .

Les spécifications de format sont maintenues et développées par le PCI-SIG (PCI Special Interest Group ) – un groupe de plus de 900 entreprises qui maintient également les spécifications PCI conventionnelles .

Architecture

Exemple de topologie PCI Express :

Exemple de topologie PCI Express :

les “boîtes de jonction” blanches représentent les ports en aval du périphérique PCI Express, tandis que les grises représentent les ports en amont. [5] : 7

Carte PCI Express × 1 contenant un commutateur PCI Express (couvert par un petit dissipateur thermique ), qui crée plusieurs points de terminaison à partir d’un point de terminaison et permet à plusieurs périphériques de le partager

Carte PCI Express × 1 contenant un commutateur PCI Express (couvert par un petit dissipateur thermique ), qui crée plusieurs points de terminaison à partir d’un point de terminaison et permet à plusieurs périphériques de le partager

Les emplacements PCIe sur une carte mère sont souvent étiquetés avec le nombre de voies PCIe dont ils disposent. Parfois, ce qui peut sembler être une grande fente peut n’avoir que quelques voies. Par exemple, un emplacement x16 avec seulement 4 voies PCIe est assez courant. [6]

Les emplacements PCIe sur une carte mère sont souvent étiquetés avec le nombre de voies PCIe dont ils disposent. Parfois, ce qui peut sembler être une grande fente peut n’avoir que quelques voies. Par exemple, un emplacement x16 avec seulement 4 voies PCIe est assez courant. [6]

Conceptuellement, le bus PCI Express est un remplacement série à grande vitesse de l’ancien bus PCI/PCI-X. [7] L’une des principales différences entre le bus PCI Express et l’ancien PCI est la topologie du bus ; PCI utilise une architecture de bus parallèle partagé , dans laquelle l’hôte PCI et tous les périphériques partagent un ensemble commun d’adresses, de données et de lignes de contrôle. En revanche, PCI Express est basé sur une topologie point à point , avec des liaisons série séparées connectant chaque périphérique au complexe racine(héberger). En raison de sa topologie de bus partagé, l’accès à l’ancien bus PCI est arbitré (dans le cas de plusieurs maîtres) et limité à un maître à la fois, dans une seule direction. De plus, l’ancien schéma de synchronisation PCI limite l’horloge du bus au périphérique le plus lent sur le bus (quels que soient les périphériques impliqués dans la transaction de bus). En revanche, une liaison de bus PCI Express prend en charge la communication en Duplex intégral entre deux points d’extrémité, sans limitation inhérente à l’accès simultané sur plusieurs points d’extrémité.

En termes de protocole de bus, la communication PCI Express est encapsulée dans des paquets. Le travail de mise en paquet et de dépaquettage du trafic de données et de messages d’état est géré par la couche de transaction du port PCI Express (décrit plus loin). Des différences radicales dans la signalisation électrique et le protocole de bus nécessitent l’utilisation d’un facteur de forme mécanique et de connecteurs d’extension différents (et donc, de nouvelles cartes mères et de nouvelles cartes d’adaptation); Les emplacements PCI et les emplacements PCI Express ne sont pas interchangeables. Au niveau logiciel, PCI Express préserve la rétrocompatibilité avec PCI ; Le logiciel système PCI hérité peut détecter et configurer les nouveaux périphériques PCI Express sans prise en charge explicite de la norme PCI Express, bien que les nouvelles fonctionnalités PCI Express soient inaccessibles.

La liaison PCI Express entre deux périphériques peut varier en taille de 1 à 16 voies . Dans une liaison multi-voies, les données en paquets sont réparties sur plusieurs voies et le Débit maximal de données évolue avec la largeur globale de la liaison. Le nombre de voies est automatiquement négocié lors de l’initialisation de l’appareil et peut être limité par l’un ou l’autre des terminaux. Par exemple, une carte PCI Express à voie unique (×1) peut être insérée dans un emplacement à plusieurs voies (×4, ×8, etc.), et le cycle d’initialisation négocie automatiquement le nombre de voies le plus élevé mutuellement pris en charge. Le lien peut se configurer dynamiquement pour utiliser moins de voies, offrant une tolérance aux pannes en cas de mauvaises voies ou de voies non fiables. La norme PCI Express définit des largeurs de liaison de ×1, ×2, ×4, ×8 et ×16. Jusqu’à et y compris PCIe 5.0, les liaisons ×12 et ×32 étaient également définies mais jamais utilisées.[8] Cela permet au bus PCI Express de servir à la fois les applications sensibles aux coûts où un Débit élevé n’est pas nécessaire, et les applications critiques en termes de performances telles que les graphiques 3D, la mise en réseau ( 10 Gigabit Ethernet ou multiport Gigabit Ethernet ) et le stockage d’entreprise ( SAS ou Fibre Channel ). Les emplacements et les connecteurs ne sont définis que pour un sous-ensemble de ces largeurs, avec des largeurs de liaison intermédiaires utilisant la taille d’emplacement physique immédiatement supérieure.

À titre de référence, un périphérique PCI-X (133 MHz 64 bits) et un périphérique PCI Express 1.0 utilisant quatre voies (×4) ont à peu près le même taux de transfert unidirectionnel maximal de 1 064 Mo/s. Le bus PCI Express a le potentiel de mieux fonctionner que le bus PCI-X dans les cas où plusieurs périphériques transfèrent des données simultanément, ou si la communication avec le périphérique PCI Express est bidirectionnelle .

Interconnexion

Une liaison PCI Express entre deux périphériques consiste en une ou plusieurs voies, qui sont des canaux doubles simplex utilisant deux paires de signalisation différentielles . [5] : 3

Une liaison PCI Express entre deux périphériques consiste en une ou plusieurs voies, qui sont des canaux doubles simplex utilisant deux paires de signalisation différentielles . [5] : 3

Les périphériques PCI Express communiquent via une connexion logique appelée interconnexion [9] ou lien . Un lien est un canal de communication point à point entre deux ports PCI Express permettant à chacun d’entre eux d’envoyer et de recevoir des requêtes PCI ordinaires (configuration, E/S ou lecture/écriture mémoire) et des interruptions ( INTx , MSI ou MSI-X ) . Au niveau physique, un lien est composé d’une ou plusieurs voies . [9] Les périphériques à faible vitesse (tels qu’une carte Wi-Fi 802.11 ) utilisent une liaison à une seule voie (×1), tandis qu’un adaptateur graphique utilise généralement une liaison à 16 voies (×16) beaucoup plus large et donc plus rapide.

voie

Une voie est composée de deux paires de signalisation différentielles , une paire pour recevoir des données et l’autre pour transmettre. Ainsi, chaque voie est composée de quatre fils ou traces de signal . Conceptuellement, chaque voie est utilisée comme un Flux d’octets en Duplex intégral , transportant des paquets de données au format “octet” à huit bits simultanément dans les deux sens entre les extrémités d’une liaison. [10] Les liaisons PCI Express physiques peuvent contenir 1, 4, 8 ou 16 voies. [11] [5] : 4, 5 [9] Le nombre de voies est écrit avec un préfixe “×” (par exemple, “×8” représente une carte ou un emplacement à huit voies), ×16 étant la plus grande taille en commun utiliser. [12]Les dimensions des voies sont également désignées par les termes “largeur” ou “par”, par exemple, une fente à huit voies pourrait être appelée “par 8” ou “8 voies de large”.

Pour les tailles de cartes mécaniques, voir ci- dessous .

Bus série

| Apprendre encore plus Cette section ne cite aucune source . ( mars 2018 ) Please help improve this section by adding citations to reliable sources. Unsourced material may be challenged and removed. (Learn how and when to remove this template message) |

L’architecture de bus série lié a été choisie par rapport au bus parallèle traditionnel en raison des limitations inhérentes à ce dernier, notamment le fonctionnement Semi-duplex , le nombre de signaux excessif et la bande passante intrinsèquement plus faible en raison du décalage temporel . Le décalage de synchronisation résulte de signaux électriques séparés dans une interface parallèle traversant des conducteurs de différentes longueurs, sur des couches de carte de circuit imprimé (PCB) potentiellement différentes et à des vitesses de signal éventuellement différentes . Bien qu’il soit transmis simultanément en un seul mot, les signaux sur une interface parallèle ont des durées de trajet différentes et arrivent à destination à des moments différents. Lorsque la période d’horloge de l’interface est inférieure à la plus grande différence de temps entre les arrivées de signal, la récupération du mot transmis n’est plus possible. Étant donné que le décalage temporel sur un bus parallèle peut atteindre quelques nanosecondes, la limitation de bande passante qui en résulte est de l’ordre de centaines de mégahertz.

Topologies hautement simplifiées de l’interface PCI partagée (parallèle) héritée et de l’interface série point à point PCIe [13]

Topologies hautement simplifiées de l’interface PCI partagée (parallèle) héritée et de l’interface série point à point PCIe [13]

Une interface série ne présente pas de décalage temporel car il n’y a qu’un seul signal différentiel dans chaque direction dans chaque voie, et il n’y a pas de signal d’horloge externe puisque les informations d’horloge sont intégrées dans le signal série lui-même. En tant que telles, les limitations de bande passante typiques sur les signaux série se situent dans la plage multi-gigahertz. PCI Express est un exemple de la tendance générale au remplacement des bus parallèles par des interconnexions série ; d’autres exemples incluent Serial ATA (SATA), USB , Serial Attached SCSI (SAS), FireWire (IEEE 1394) et RapidIO . En vidéo numérique, les exemples couramment utilisés sont DVI , HDMI et DisplayPort .

La conception série multicanal augmente la flexibilité grâce à sa capacité à allouer moins de voies aux appareils plus lents.

Facteurs de forme

PCI Express (standard)

SSD flash Intel P3608 NVMe, carte d’extension PCI-E

SSD flash Intel P3608 NVMe, carte d’extension PCI-E

Une carte PCI Express s’insère dans un emplacement de sa taille physique ou plus (avec × 16 comme le plus grand utilisé), mais peut ne pas tenir dans un emplacement PCI Express plus petit; par exemple, une carte ×16 peut ne pas tenir dans un emplacement ×4 ou ×8. Certains emplacements utilisent des sockets ouverts pour permettre des cartes physiquement plus longues et négocier la meilleure connexion électrique et logique disponible.

Le nombre de voies réellement connectées à un emplacement peut également être inférieur au nombre pris en charge par la taille physique de l’emplacement. Un exemple est un emplacement ×16 qui fonctionne à ×4, qui accepte n’importe quelle carte ×1, ×2, ×4, ×8 ou ×16, mais ne fournit que quatre voies. Sa spécification peut se lire comme “×16 (mode ×4)”, tandis que la notation “×mécanique @ ×électrique” (“×16 @ ×4”) est également courante. L’avantage est que ces emplacements peuvent accueillir une plus grande gamme de cartes PCI Express sans nécessiter de matériel de carte mère pour prendre en charge le taux de transfert complet. Les tailles mécaniques standard sont ×1, ×4, ×8 et ×16. Les cartes avec un nombre différent de voies doivent utiliser la taille mécanique supérieure suivante (c’est-à-dire qu’une carte ×2 utilise la taille ×4, ou une carte ×12 utilise la taille ×16).

Les cartes elles-mêmes sont conçues et fabriquées en différentes tailles. Par exemple, les disques SSD qui se présentent sous la forme de cartes PCI Express utilisent souvent HHHL (demi-hauteur, demi-longueur) et FHHL (pleine hauteur, demi-longueur) pour décrire les dimensions physiques de la carte. [14] [15]

| Type de carte PCI | Dimensions hauteur × longueur × largeur, maximum | |

|---|---|---|

| (mm) | (dans) | |

| Toute la longueur | 111,15 × 312,00 × 20,32 | 4,376 × 12,283 × 0,8 |

| Demi-longueur | 111,15 × 167,65 × 20,32 | 4,376 × 0 6,600 × 0,8 |

| Profil bas/mince | 0 68,90 × 167,65 × 20,32 | 2,731 × 0 6,600 × 0,8 |

Facteurs de forme de Carte vidéo non standard

Les cartes vidéo de jeu modernes (depuis environ 2012 [16] ) dépassent généralement la hauteur et l’épaisseur spécifiées dans la norme PCI Express, en raison du besoin de ventilateurs de refroidissement plus performants et plus silencieux , car les cartes vidéo de jeu émettent souvent des centaines de watts de Chauffer. [17] Les boîtiers d’ordinateurs modernes sont souvent plus larges pour accueillir ces cartes plus hautes, mais pas toujours. Étant donné que les cartes pleine longueur (312 mm) sont rares, les boîtiers modernes ne peuvent parfois pas s’y adapter. L’épaisseur de ces cartes occupe aussi typiquement l’espace de 2 slots PCIe. En fait, même la méthodologie de mesure des cartes varie d’un fournisseur à l’autre, certains incluant la taille du support métallique dans les dimensions et d’autres non.

Par exemple, une carte Sapphire 2020 mesure 135 mm de hauteur (hors support métallique), ce qui dépasse la hauteur standard PCIe de 28 mm. [18] Une autre carte de XFX mesure 55 mm d’épaisseur (soit 2,7 slots PCI à 20,32 mm), occupant 3 slots PCIe. [19] La Carte vidéo Asus GeForce RTX 3080 10 Go STRIX GAMING OC est une carte à deux emplacements qui a des dimensions de 318,5 mm × 140,1 mm × 57,8 mm, dépassant respectivement la longueur, la hauteur et l’épaisseur maximales de PCI Express. [20]

Brochage

Le tableau suivant identifie les conducteurs de chaque côté du connecteur de bord sur une carte PCI Express. Le côté soudure de la carte de circuit imprimé (PCB) est le côté A et le côté composant est le côté B. [21] Les broches PRSNT1# et PRSNT2# doivent être légèrement plus courtes que les autres, pour s’assurer qu’une carte enfichée à chaud est complètement insérée. La broche WAKE # utilise la pleine tension pour réveiller l’ordinateur, mais doit être tirée vers le haut de l’alimentation de veille pour indiquer que la carte est capable de réveil. [22]

| Broche | Côté B | Face A | La description | Broche | Côté B | Face A | La description |

|---|---|---|---|---|---|---|---|

| 0 1 | +12V | PRSNT1# | Doit se connecter à la broche PRSNT2 # la plus éloignée | 50 | HSOp(8) | Réservé | La voie 8 transmet des données, + et – |

| 0 2 | +12V | +12V | Broches d’alimentation principale | 51 | HSOn(8) | Sol | |

| 0 3 | +12V | +12V | 52 | Sol | HSI(8) | La voie 8 reçoit des données, + et – | |

| 0 4 | Sol | Sol | 53 | Sol | HSIn(8) | ||

| 0 5 | SMCLK | TCK | Broches des ports SMBus et JTAG | 54 | HSOp(9) | Sol | La voie 9 transmet des données, + et – |

| 0 6 | SMDAT | TDI | 55 | HSOn(9) | Sol | ||

| 0 7 | Sol | TDO | 56 | Sol | HSIp(9) | La voie 9 reçoit des données, + et – | |

| 0 8 | +3,3 V | SMT | 57 | Sol | HSIn(9) | ||

| 0 9 | TRST# | +3,3 V | 58 | HSOp(10) | Sol | La voie 10 transmet des données, + et – | |

| dix | +3,3 V aux | +3,3 V | Alimentation de secours | 59 | HSOn(10) | Sol | |

| 11 | RÉVEILLER# | PREST# | Réactivation du lien ; réinitialisation fondamentale [23] | 60 | Sol | HSIp(10) | La voie 10 reçoit des données, + et – |

| Encoche clé | 61 | Sol | HSIn(10) | ||||

| 12 | CLKREQ# [24] | Sol | Signal de demande d’horloge | 62 | HSOp(11) | Sol | La voie 11 transmet des données, + et – |

| 13 | Sol | REFLK+ | Paire différentielle d’horloge de référence | 63 | HSOn(11) | Sol | |

| 14 | HSOp(0) | REFLK− | La voie 0 transmet les données, + et – | 64 | Sol | HSIP(11) | La voie 11 reçoit des données, + et – |

| 15 | HSOn(0) | Sol | 65 | Sol | HSIn(11) | ||

| 16 | Sol | HSIp(0) | La voie 0 reçoit des données, + et – | 66 | HSOp(12) | Sol | La voie 12 transmet des données, + et – |

| 17 | PRSNT2# | HSIn(0) | 67 | HSOn(12) | Sol | ||

| 18 | Sol | Sol | 68 | Sol | HSIP(12) | La voie 12 reçoit des données, + et – | |

| Les cartes PCI Express ×1 se terminent à la broche 18 | 69 | Sol | HSIn(12) | ||||

| 19 | HSOp(1) | Réservé | La voie 1 transmet les données, + et – | 70 | HSOp(13) | Sol | La voie 13 transmet des données, + et – |

| 20 | HSOn(1) | Sol | 71 | HSOn(13) | Sol | ||

| 21 | Sol | HSI(1) | La voie 1 reçoit des données, + et – | 72 | Sol | HSIP(13) | La voie 13 reçoit des données, + et – |

| 22 | Sol | HSIn(1) | 73 | Sol | HSIn(13) | ||

| 23 | HSOp(2) | Sol | La voie 2 transmet les données, + et – | 74 | HSOp(14) | Sol | La voie 14 transmet des données, + et – |

| 24 | HSOn(2) | Sol | 75 | HSOn(14) | Sol | ||

| 25 | Sol | HSip(2) | La voie 2 reçoit des données, + et – | 76 | Sol | HSIP(14) | La voie 14 reçoit des données, + et – |

| 26 | Sol | HSIn(2) | 77 | Sol | HSIn(14) | ||

| 27 | HSOp(3) | Sol | La voie 3 transmet les données, + et – | 78 | HSOp(15) | Sol | La voie 15 transmet des données, + et – |

| 28 | HSOn(3) | Sol | 79 | HSOn(15) | Sol | ||

| 29 | Sol | HSip(3) | La voie 3 reçoit des données, + et – | 80 | Sol | HSIP(15) | La voie 15 reçoit des données, + et – |

| 30 | PWRBRK# [25] | HSIn(3) | 81 | PRSNT2# | HSIn(15) | ||

| 31 | PRSNT2# | Sol | 82 | Réservé | Sol | ||

| 32 | Sol | Réservé | |||||

| Les cartes PCI Express ×4 se terminent à la broche 32 | |||||||

| 33 | HSOp(4) | Réservé | La voie 4 transmet les données, + et – | ||||

| 34 | HSOn(4) | Sol | |||||

| 35 | Sol | HSI(4) | La voie 4 reçoit des données, + et – | ||||

| 36 | Sol | HSIn(4) | |||||

| 37 | HSOp(5) | Sol | La voie 5 transmet les données, + et – | ||||

| 38 | HSOn(5) | Sol | |||||

| 39 | Sol | HSIp(5) | La voie 5 reçoit des données, + et – | ||||

| 40 | Sol | HSIn(5) | |||||

| 41 | HSOp(6) | Sol | La voie 6 transmet des données, + et – | ||||

| 42 | HSOn(6) | Sol | |||||

| 43 | Sol | HSIp(6) | La voie 6 reçoit des données, + et – | Légende | |||

| 44 | Sol | HSIn(6) | Broche de terre | Référence zéro volt | |||

| 45 | HSOp(7) | Sol | La voie 7 transmet des données, + et – | Broche d’alimentation | Alimente la carte PCIe | ||

| 46 | HSOn(7) | Sol | Broche carte-hôte | Signal de la carte à la carte mère | |||

| 47 | Sol | HSI(7) | La voie 7 reçoit des données, + et – | Broche hôte-carte | Signal de la carte mère à la carte | ||

| 48 | PRSNT2# | HSIn(7) | Vidange ouverte | Peut être tiré vers le bas ou détecté par plusieurs cartes | |||

| 49 | Sol | Sol | Broche de détection | Liés ensemble sur carte | |||

| Les cartes PCI Express ×8 se terminent à la broche 49 | Réservé | Non utilisé actuellement, ne pas connecter |

Pouvoir

Connecteurs d’alimentation à 8 broches (gauche) et 6 broches (droite) utilisés sur les cartes PCI Express

Connecteurs d’alimentation à 8 broches (gauche) et 6 broches (droite) utilisés sur les cartes PCI Express

Toutes les cartes PCI Express peuvent consommer jusqu’à3 A à+ 3,3V (9,9 W ). La quantité de +12 V et la puissance totale qu’ils peuvent consommer dépendent du type de carte : [26] : 35–36 [27]

- Les cartes ×1 sont limitées à 0,5 A sous +12 V (6 W) et 10 W combinés.

- Les cartes ×4 et plus sont limitées à 2,1 A à +12 V (25 W) et 25 W combinés.

- Une carte pleine taille ×1 peut tirer jusqu’aux limites de 25 W après l’initialisation et la configuration logicielle en tant que “périphérique haute puissance”.

- Une carte graphique pleine taille ×16 [22] peut consommer jusqu’à 5,5 A à +12 V (66 W) et 75 W combinés après initialisation et configuration logicielle en tant que “dispositif haute puissance”.

Les connecteurs en option ajoutent 75 W (6 broches) ou 150 W (8 broches) d’alimentation +12 V pour un maximum de 300 W au total ( 2 × 75 W + 1 × 150 W ).

- La broche Sense0 est connectée à la terre par le câble ou l’alimentation, ou flotte à bord si le câble n’est pas connecté.

- La broche Sense1 est connectée à la terre par le câble ou l’alimentation, ou flotte à bord si le câble n’est pas connecté.

Certaines cartes utilisent deux connecteurs à 8 broches, mais cela n’a pas encore été normalisé en 2018 [update], par conséquent, ces cartes ne doivent pas porter le logo officiel PCI Express. Cette configuration autorise 375 W au total ( 1 × 75 W + 2 × 150 W ) et sera probablement standardisée par PCI-SIG avec la norme PCI Express 4.0 [ nécessite une mise à jour ] . Le connecteur PCI Express à 8 broches peut être confondu avec le connecteur EPS12V , qui est principalement utilisé pour alimenter les systèmes SMP et multicœurs. Les connecteurs d’alimentation sont des variantes des connecteurs de la série Molex Mini-Fit Jr.. [28]

| Épingles | Femelle/embase sur câble PS |

Embase mâle/à angle droit sur PCB |

|

|---|---|---|---|

| 6 broches | 45559-0002 | 45558-0003 | |

| 8 broches | 45587-0004 | 45586-0005, 45586-0006 | |

| Connecteur d’alimentation à 6 broches (75 W) [29] | Connecteur d’alimentation à 8 broches (150 W) [30] [31] [32] | |

|

| Broche | La description | Broche | La description |

| 1 | +12V | 1 | +12V |

| 2 | Non connecté (généralement +12 V également) | 2 | +12V |

| 3 | +12V | 3 | +12V |

| 4 | Sense1 (connecté à 8 broches [A] ) | ||

| 4 | Sol | 5 | Sol |

| 5 | Sens | 6 | Sense0 (connecté à 6 ou 8 broches) |

| 6 | Sol | 7 | Sol |

| 8 | Sol |

- ^ Lorsqu’un connecteur à 6 broches est branché dans une prise à 8 broches, la carte est avertie par un Sense1 manquant qu’elle ne peut utiliser que jusqu’à 75 W.

Mini-carte PCI Express

Une Mini Carte WLAN PCI Express et son connecteur

Une Mini Carte WLAN PCI Express et son connecteur

Cartes MiniPCI et MiniPCI Express en comparaison

Cartes MiniPCI et MiniPCI Express en comparaison

La mini- carte PCI Express (également appelée Mini PCI Express , Mini PCIe , Mini PCI-E , mPCIe et PEM ), basée sur PCI Express, remplace le facteur de forme Mini PCI . Il est développé par le PCI-SIG . Le périphérique hôte prend en charge à la fois la connectivité PCI Express et USB 2.0, et chaque carte peut utiliser l’une ou l’autre norme. La plupart des ordinateurs portables construits après 2005 utilisent PCI Express pour les cartes d’extension ; Cependant, à partir de 2015 [update], de nombreux fournisseurs s’orientent vers l’utilisation du nouveau facteur de forme M.2 à cette fin.

En raison de dimensions différentes, les mini-cartes PCI Express ne sont pas physiquement compatibles avec les emplacements PCI Express standard de taille normale ; cependant, il existe des adaptateurs passifs qui permettent de les utiliser dans des emplacements pleine grandeur. [33]

Dimensions physiques

Les dimensions des mini-cartes PCI Express sont de 30 mm × 50,95 mm (largeur × longueur) pour une mini-carte complète. On retrouve un connecteur de tranche 52 broches , composé de deux rangées en quinconce au pas de 0,8 mm. Chaque rangée a huit contacts, un espace équivalent à quatre contacts, puis 18 autres contacts. Les planches ont une épaisseur de 1,0 mm, à l’exclusion des composants. Une “Half Mini Card” (parfois abrégée en HMC) est également spécifiée, ayant environ la moitié de la longueur physique de 26,8 mm.

Interface électrique

Les connecteurs de bord de la mini-carte PCI Express fournissent plusieurs connexions et bus :

- PCI Express ×1 (avec SMBus)

- USB 2.0

- Câbles vers les voyants de diagnostic pour l’état du réseau sans fil (c’est-à-dire Wi-Fi ) sur le châssis de l’ordinateur

- Carte SIM pour applications GSM et WCDMA (signaux UIM sur spec.)

- Extension future pour une autre voie PCIe

- Alimentation 1,5 V et 3,3 V

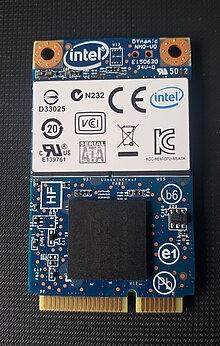

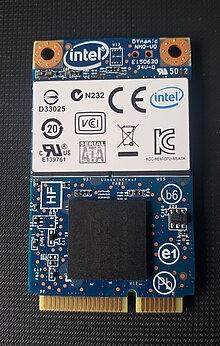

Variante mini-SATA (mSATA)

Un SSD Intel mSATA

Un SSD Intel mSATA

Malgré le partage du facteur de forme Mini PCI Express, un emplacement mSATA n’est pas nécessairement électriquement compatible avec Mini PCI Express. Pour cette raison, seuls certains ordinateurs portables sont compatibles avec les disques mSATA. La plupart des systèmes compatibles sont basés sur l’architecture de processeur Sandy Bridge d’Intel, utilisant la plate-forme Huron River. Les ordinateurs portables tels que les séries ThinkPad T, W et X de Lenovo, sortis en mars-avril 2011, prennent en charge une carte SSD mSATA dans leur emplacement pour carte WWAN . Le ThinkPad Edge E220s/E420s et le Lenovo IdeaPad Y460/Y560/Y570/Y580 prennent également en charge mSATA. [34] Au contraire, la série L, entre autres, ne peut prendre en charge que les cartes M.2 utilisant la norme PCIe dans l’emplacement WWAN.

Certains ordinateurs portables (notamment l’ Asus Eee PC , l’ Apple MacBook Air et les Dell mini9 et mini10) utilisent une variante de la mini-carte PCI Express comme SSD . Cette variante utilise les broches réservées et plusieurs broches non réservées pour implémenter le relais d’interface SATA et IDE, en ne conservant que l’USB, les lignes de masse et parfois le bus principal PCIe × 1 intact. [35] Cela rend les lecteurs flash et à semi-conducteurs “miniPCIe” vendus pour les netbooks largement incompatibles avec les véritables implémentations PCI Express Mini.

De plus, le SSD miniPCIe Asus typique mesure 71 mm de long, ce qui fait que le modèle Dell 51 mm est souvent (incorrectement) appelé demi-longueur. Un véritable SSD Mini PCIe de 51 mm a été annoncé en 2009, avec deux couches de PCB empilées qui permettent une plus grande capacité de stockage. La conception annoncée préserve l’interface PCIe, la rendant compatible avec le slot mini PCIe standard. Aucun produit fonctionnel n’a encore été développé.

Intel propose de nombreuses cartes mères pour PC de bureau avec un emplacement mini-carte PCIe × 1 qui ne prennent généralement pas en charge les SSD mSATA. Une liste des cartes mères qui prennent nativement en charge mSATA dans le logement mini-carte PCIe ×1 (généralement multiplexé avec un port SATA) est fournie sur le site de support Intel. [36]

PCI Express M.2

M.2 remplace la norme mSATA et Mini PCIe. [37] Les interfaces de bus informatique fournies via le connecteur M.2 sont PCI Express 3.0 (jusqu’à quatre voies), Serial ATA 3.0 et USB 3.0 (un seul port logique pour chacun des deux derniers). Il appartient au fabricant de l’hôte ou du périphérique M.2 de choisir les interfaces à prendre en charge, en fonction du niveau souhaité de prise en charge de l’hôte et du type de périphérique.

Câblage externe PCI Express

Les spécifications du câblage externe PCI Express (également connu sous le nom de PCI Express externe , PCI Express câblé ou ePCIe ) ont été publiées par le PCI-SIG en février 2007. [38] [39]

Des câbles et connecteurs standard ont été définis pour des largeurs de liaison ×1, ×4, ×8 et ×16, avec un taux de transfert de 250 Mo/s par voie. Le PCI-SIG s’attend également à ce que la norme évolue pour atteindre 500 Mo/s, comme dans le PCI Express 2.0. Un exemple des utilisations de Cabled PCI Express est un boîtier métallique, contenant un certain nombre d’emplacements PCIe et des circuits adaptateurs PCIe à ePCIe. Ce dispositif ne serait pas possible sans la spécification ePCIe.

PCI Express OCuLink

OCuLink (pour “optical-copper link”, puisque Cu est le symbole chimique du cuivre ) est une extension de la “version câble de PCI Express”, agissant comme un concurrent de la version 3 de l’interface Thunderbolt. La version 1.0 d’OCuLink, publiée en octobre 2015, prend en charge jusqu’à PCIe 3.0 ×4 voies (8 GT/s , 3,9 Go/s) sur un câblage en cuivre ; une version fibre optique pourrait apparaître dans le futur.

Dans sa dernière version OCuLink-2, il prend en charge jusqu’à 16 Go/s (PCIe 4.0 ×8) [40] tandis que la bande passante maximale d’un câble Thunderbolt 4 pleine vitesse est de 5 Go/s. Certains fournisseurs peuvent concevoir leur produit de connecteur pour être en mesure de prendre en charge la prochaine génération de PCI Express 5.0 fonctionnant à 32 GT/s par voie pour assurer l’avenir et minimiser les coûts de développement au cours des prochaines années. [40] Initialement, PCI-SIG prévoyait d’introduire OCuLink dans les ordinateurs portables pour la connexion de puissants boîtiers GPU externes. Il s’est avéré être une utilisation rare. Au lieu de cela, OCuLink est devenu populaire pour les interconnexions PCIe dans les serveurs. [41]

Formes dérivées

De nombreux autres facteurs de forme utilisent ou sont capables d’utiliser PCIe. Ceux-ci inclus:

- Carte de faible hauteur

- ExpressCard : Successeur du facteur de forme PC Card (avec ×1 PCIe et USB 2.0 ; enfichable à chaud)

- PCI Express ExpressModule : un facteur de forme modulaire enfichable à chaud défini pour les serveurs et les stations de travail

- Carte XQD : Une norme de carte flash basée sur PCI Express par la CompactFlash Association avec ×2 PCIe

- Carte CFexpress : Une carte flash basée sur PCI Express par la CompactFlash Association dans trois facteurs de forme prenant en charge 1 à 4 voies PCIe

- Carte SD : Le bus SD Express , introduit dans la version 7.0 de la spécification SD utilise une liaison PCIe ×1

- XMC : Similaire au facteur de forme CMC / PMC (VITA 42.3)

- AdvancedTCA : Un complément à CompactPCI pour les applications plus importantes ; prend en charge les topologies de fond de panier série

- AMC : Un complément à la spécification AdvancedTCA ; prend en charge les modules de processeur et d’E/S sur les cartes ATCA (×1, ×2, ×4 ou ×8 PCIe).

- FeaturePak : Un petit format de carte d’extension (43 mm × 65 mm) pour les applications embarquées et à petit facteur de forme, qui implémente deux ×1 liaisons PCIe sur un connecteur haute densité avec USB, I2C et jusqu’à 100 points d’I /O

- Universal IO : Une variante de Super Micro Computer Inc conçue pour être utilisée dans des châssis montés en rack à profil bas. [42] Il a le support de connecteur inversé afin qu’il ne puisse pas tenir dans une prise PCI Express normale, mais il est compatible avec les broches et peut être inséré si le support est retiré.

- M.2 (anciennement connu sous le nom de NGFF)

- M-PCIe apporte PCIe 3.0 aux appareils mobiles (tels que les tablettes et les smartphones), via la couche physique M-PHY . [43] [44]

- U.2 (anciennement connu sous le nom de SFF-8639)

Le connecteur d’emplacement PCIe peut également transporter des protocoles autres que PCIe. Certains chipsets Intel de la série 9xx prennent en charge la sortie vidéo numérique série , une technologie propriétaire qui utilise un emplacement pour transmettre les signaux vidéo à partir des graphiques intégrés du processeur hôte au lieu de PCIe, à l’aide d’un complément pris en charge.

Le protocole de couche de transaction PCIe peut également être utilisé sur d’autres interconnexions, qui ne sont pas électriquement PCIe :

- Thunderbolt : Une norme d’interconnexion libre de droits d’Intel qui combine les protocoles DisplayPort et PCIe dans un facteur de forme compatible avec Mini DisplayPort . Thunderbolt 3.0 combine également USB 3.1 et utilise le facteur de forme USB-C par opposition au Mini DisplayPort.

- USB4

Historique et révisions

Au début du développement, PCIe était initialement appelé HSI (pour High Speed Interconnect ) et a subi un changement de nom en 3GIO (pour 3rd Generation I/O ) avant de finalement s’installer sur son nom PCI-SIG PCI Express . Un groupe de travail technique nommé Arapaho Work Group (AWG) a élaboré la norme. Pour les ébauches initiales, l’AWG était composé uniquement d’ingénieurs Intel ; par la suite, l’AWG s’est élargi pour inclure des partenaires de l’industrie.

Depuis, PCIe a subi plusieurs révisions importantes et mineures, améliorant les performances et d’autres fonctionnalités.

| Version | Introduit _ |

Indicatif de ligne | Taux de transfert

par voie [i] [ii] |

Débit [i] [iii] | |||||

|---|---|---|---|---|---|---|---|---|---|

| ×1 | ×2 | ×4 | ×8 | ×16 | |||||

| 1.0 | 2003 | NRZ | 8b/10b | 2,5 GT/s | 0,250 Go/s | 0,500 Go/s | 1.000 Go/s | 2.000 Go/s | 4.000 Go/s |

| 2.0 | 2007 | 8b/10b | 5,0 GT/s | 0,500 Go/s | 1.000 Go/s | 2.000 Go/s | 4.000 Go/s | 8.000 Go/s | |

| 3.0 | 2010 | 128b/130b | 8,0 GT/s | 0,985 Go/s | 1.969 Go/s | 3,938 Go/s | 0 7,877 Go/s | 15,754 Go/s | |

| 4.0 | 2017 | 128b/130b | 16,0 GT/s | 1.969 Go/s | 3,938 Go/s | 0 7,877 Go/s | 15,754 Go/s | 0 31.508 Go/s | |

| 5.0 | 2019 | 128b/130b | 32,0 GT/s | 3,938 Go/s | 0 7,877 Go/s | 15,754 Go/s | 31.508 Go/s | 63.015 Go/s | |

| 6.0 | 2022 | FEC PAM-4 | 242B/256B FLIT |

64,0 GT/s 32,0 Gbd |

7,563 Go/s | 15,125 Go/s | 30.250 Go/s | 60.500 Go/s | 121.000 Go/s |

Remarques

- ^ a b Dans chaque direction (chaque voie est un double canal simplex).

- ^ Le taux de transfert fait référence au Débit binaire série codé ; 2,5 GT/s signifie un Débit de données série de 2,5 Gbit/s.

- ^ Le Débit indique la bande passante non codée (sans surcharge de codage 8b/10b, 128b/130b ou 242B/256B). Le taux de transfert PCIe 1.0 de 2,5 GT/s par voie signifie un Débit binaire série de 2,5 Gbit/s correspondant à un Débit de 2,0 Gbit/s ou 250 Mo/s avant l’encodage 8b/10b.

PCI Express 1.0a

En 2003, PCI-SIG a introduit PCIe 1.0a, avec un Débit de données par voie de 250 Mo/s et un taux de transfert de 2,5 gigatransferts par seconde (GT/s).

Le taux de transfert est exprimé en transferts par seconde au lieu de bits par seconde car le nombre de transferts inclut les bits supplémentaires, qui ne fournissent pas de Débit supplémentaire ; [47] PCIe 1.x utilise un schéma de codage 8b/10b , ce qui entraîne une surcharge de 20 % (= 2/10) sur la bande passante brute du canal. [48] Ainsi, dans la terminologie PCIe, le taux de transfert fait référence au Débit binaire encodé : 2,5 GT/s correspond à 2,5 Gbps sur la liaison série encodée. Cela correspond à 2,0 Gbit/s de données précodées ou 250 Mo/s, ce que l’on appelle le Débit en PCIe.

PCI Express 1.1

En 2005, PCI-SIG [49] a introduit PCIe 1.1. Cette spécification mise à jour comprend des clarifications et plusieurs améliorations, mais est entièrement compatible avec PCI Express 1.0a. Aucune modification n’a été apportée au Débit de données.

PCI Express 2.0

Une carte d’extension PCI Express 2.0 qui fournit une connectivité USB 3.0. [c]

Une carte d’extension PCI Express 2.0 qui fournit une connectivité USB 3.0. [c]

PCI-SIG a annoncé la disponibilité de la spécification PCI Express Base 2.0 le 15 janvier 2007. [50] La norme PCIe 2.0 double le taux de transfert par rapport à PCIe 1.0 à 5 GT/s et le Débit par voie passe de 250 Mo/s à 500 Mo/s. Par conséquent, un connecteur PCIe à 16 voies (×16) peut prendre en charge un Débit cumulé allant jusqu’à 8 Go/s.

Les emplacements de carte mère PCIe 2.0 sont entièrement rétrocompatibles avec les cartes PCIe v1.x. Les cartes PCIe 2.0 sont également généralement rétrocompatibles avec les cartes mères PCIe 1.x, en utilisant la bande passante disponible de PCI Express 1.1. Dans l’ensemble, les cartes graphiques ou les cartes mères conçues pour la v2.0 fonctionnent, les autres étant la v1.1 ou la v1.0a.

Le PCI-SIG a également déclaré que PCIe 2.0 présente des améliorations du protocole de transfert de données point à point et de son architecture logicielle. [51]

Le premier chipset compatible PCIe 2.0 d’ Intel était le X38 et les cartes ont commencé à être expédiées par divers fournisseurs ( Abit , Asus , Gigabyte ) à partir du 21 octobre 2007. [52] AMD a commencé à prendre en charge PCIe 2.0 avec sa série de chipsets AMD 700 et nVidia a commencé avec le MCP72 . [53] Tous les chipsets précédents d’Intel, y compris le chipset Intel P35 , prenaient en charge PCIe 1.1 ou 1.0a. [54]

Comme 1.x, PCIe 2.0 utilise un schéma d’ encodage 8b/10b , fournissant ainsi, par voie, un maximum effectif de 4 Gbit/s. taux de transfert à partir de son Débit de données brutes de 5 GT/s.

PCI Express 2.1

PCI Express 2.1 (avec sa spécification datée du 4 mars 2009) prend en charge une grande partie des systèmes de gestion, de support et de dépannage prévus pour une mise en œuvre complète dans PCI Express 3.0. Cependant, la vitesse est la même que PCI Express 2.0. L’augmentation de la puissance de l’emplacement rompt la rétrocompatibilité entre les cartes PCI Express 2.1 et certaines cartes mères plus anciennes avec 1.0/1.0a, mais la plupart des cartes mères avec des connecteurs PCI Express 1.1 sont fournies avec une mise à jour du BIOS par leurs fabricants via des utilitaires pour prendre en charge la rétrocompatibilité des cartes. avec PCIe 2.1.

PCI Express 3.0

La révision 3.0 de la spécification de base PCI Express 3.0 a été rendue disponible en novembre 2010, après plusieurs retards. En août 2007, PCI-SIG a annoncé que PCI Express 3.0 assurerait un Débit binaire de 8 gigatransferts par seconde (GT/s) et qu’il serait rétrocompatible avec les implémentations PCI Express existantes. À cette époque, il a également été annoncé que la spécification finale pour PCI Express 3.0 serait retardée jusqu’au deuxième trimestre 2010. [55] Les nouvelles fonctionnalités de la spécification PCI Express 3.0 comprenaient un certain nombre d’optimisations pour améliorer la signalisation et l’intégrité des données, y compris l’émetteur et le récepteur. l’ égalisation, les améliorations PLL , la récupération des données d’horloge et les améliorations des canaux des topologies actuellement prises en charge. [56]

À la suite d’une analyse technique de six mois sur la faisabilité de la mise à l’échelle de la bande passante d’interconnexion PCI Express, l’analyse de PCI-SIG a révélé que 8 gigatransferts par seconde pourraient être fabriqués dans la technologie de processus de silicium grand public et déployés avec des matériaux et une infrastructure à faible coût existants, tout en maintenant compatibilité totale (avec un impact négligeable) avec la pile de protocoles PCI Express.

PCI Express 3.0 a mis à niveau le schéma d’encodage à 128b/130b à partir de l’ encodage 8b/10b précédent , réduisant la surcharge de bande passante de 20 % de PCI Express 2.0 à environ 1,54 % (= 2/130). Le Débit binaire de 8 GT/s de PCI Express 3.0 fournit effectivement 985 Mo/s par voie, doublant presque la bande passante de la voie par rapport à PCI Express 2.0. [46]

Le 18 novembre 2010, le Groupe d’Intérêt Spécial PCI a officiellement publié la spécification PCI Express 3.0 finalisée à ses membres pour construire des appareils basés sur cette nouvelle version de PCI Express. [57]

PCI Express 3.1

En septembre 2013, la spécification PCI Express 3.1 a été annoncée pour une sortie fin 2013 ou début 2014, consolidant diverses améliorations de la spécification PCI Express 3.0 publiée dans trois domaines: gestion de l’alimentation, performances et fonctionnalités. [44] [58] Il a été publié en novembre 2014. [59]

PCI Express 4.0

Le 29 novembre 2011, PCI-SIG a annoncé de manière préliminaire PCI Express 4.0, [60] fournissant un Débit binaire de 16 GT/s qui double la bande passante fournie par PCI Express 3.0, tout en maintenant la compatibilité ascendante et descendante à la fois dans le support logiciel et dans l’interface mécanique utilisée. [61] Les spécifications PCI Express 4.0 apportent également OCuLink-2, une alternative à Thunderbolt . La version 2 d’OCuLink a jusqu’à 16 GT/s (16 Go/s au total pour ×8 voies), [40] tandis que la bande passante maximale d’un lien Thunderbolt 3 est de 5 Go/s.

En juin 2016, Cadence, PLDA et Synopsys ont présenté la couche physique, le contrôleur, le commutateur et d’autres blocs IP PCIe 4.0 lors de la conférence annuelle des développeurs du PCI SIG. [62]

Mellanox Technologies a annoncé le premier adaptateur réseau 100 Gbit/s avec PCIe 4.0 le 15 juin 2016, [63] et le premier adaptateur réseau 200 Gbit/s avec PCIe 4.0 le 10 novembre 2016. [64]

En août 2016, Synopsys a présenté une configuration de test avec un FPGA cadencé sur une voie vers des vitesses PCIe 4.0 lors du forum des développeurs Intel . Leur propriété intellectuelle a été concédée sous licence à plusieurs entreprises prévoyant de présenter leurs puces et produits fin 2016. [65]

Lors du symposium IEEE Hot Chips en août 2016 , IBM a annoncé le premier processeur prenant en charge PCIe 4.0, POWER9 . [66] [67]

PCI-SIG a officiellement annoncé la publication de la spécification finale PCI Express 4.0 le 8 juin 2017. [68] La spécification inclut des améliorations en matière de flexibilité, d’évolutivité et de faible consommation.

Le 5 décembre 2017, IBM a annoncé le premier système avec des emplacements PCIe 4.0, Power AC922. [69] [70]

NETINT Technologies a présenté le premier SSD NVMe basé sur PCIe 4.0 le 17 juillet 2018, avant le Flash Memory Summit 2018 [71]

AMD a annoncé le 9 janvier 2019 que ses prochains processeurs basés sur Zen 2 et son chipset X570 prendraient en charge PCIe 4.0. [72] AMD avait espéré permettre une prise en charge partielle des anciens chipsets, mais l’instabilité causée par les traces de la carte mère non conformes aux spécifications PCIe 4.0 a rendu cela impossible. [73] [74]

Intel a publié ses premiers processeurs mobiles avec prise en charge PCI Express 4.0 à la mi-2020, dans le cadre de la microarchitecture Tiger Lake . [75]

PCI Express 5.0

En juin 2017, PCI-SIG a annoncé la spécification préliminaire PCI Express 5.0. [68] On s’attendait à ce que la bande passante augmente à 32 GT/s, produisant 63 Go/s dans chaque direction dans une configuration à 16 voies. Le projet de spécification devait être normalisé en 2019. [ citation nécessaire ] Initialement, 25,0 GT/s ont également été pris en compte pour la faisabilité technique.

Le 7 juin 2017 au PCI-SIG DevCon, Synopsys a enregistré la première démonstration de PCI Express 5.0 à 32GT/s. [76]

Le 31 mai 2018, PLDA a annoncé la disponibilité de son IP de contrôleur XpressRICH5 PCIe 5.0 basée sur le projet 0.7 de la spécification PCIe 5.0 le même jour. [77] [78]

Le 10 décembre 2018, le PCI SIG a publié la version 0.9 de la spécification PCIe 5.0 à ses membres [79] et le 17 janvier 2019, le PCI SIG a annoncé que la version 0.9 avait été ratifiée, la version 1.0 étant prévue pour le premier trimestre de 2019. [80]

Le 29 mai 2019, PCI-SIG a officiellement annoncé la publication de la spécification finale PCI-Express 5.0. [81] [ clarification nécessaire ]

Le 20 novembre 2019, Jiangsu Huacun a présenté le premier contrôleur PCIe 5.0 HC9001 dans un processus de fabrication de 12 nm. [82] La production a commencé en 2020.

Le 17 août 2020, IBM a annoncé le processeur POWER10 avec PCIe 5.0 et jusqu’à 32 voies par module à puce unique (SCM) et jusqu’à 64 voies par module à double puce (DCM). [83]

Le 9 septembre 2021, IBM a annoncé le serveur Power E1080 Enterprise avec une date de disponibilité prévue le 17 septembre. [84] Il peut avoir jusqu’à 16 SCM POWER10 avec un maximum de 32 emplacements par système qui peuvent agir comme PCIe 5.0 x8 ou PCIe 4.0 x16. [85] Alternativement, ils peuvent être utilisés comme emplacements PCIe 5.0 x16 pour les adaptateurs de convertisseurs optiques CXP en option se connectant aux tiroirs d’extension PCIe externes.

Le 27 octobre 2021, Intel a annoncé la famille de processeurs Intel Core de 12e génération, les premiers processeurs x86-64 grand public au monde avec une connectivité PCIe 5.0 (jusqu’à 16 voies). [86]

Le 22 mars 2022, Nvidia a annoncé le GPU Nvidia Hopper GH100, le premier GPU PCIe 5.0 au monde. [87]

PCI Express 6.0

Le 18 juin 2019, PCI-SIG a annoncé le développement de la spécification PCI Express 6.0. La bande passante devrait augmenter à 64 GT/s, produisant 128 Go/s dans chaque direction dans une configuration à 16 voies, avec une date de sortie cible de 2021. [88] La nouvelle norme utilise une modulation d’amplitude d’impulsion à 4 niveaux (PAM -4) avec une correction d’erreur directe à faible latence (FEC) à la place de la modulation sans retour à zéro (NRZ). [89] Contrairement aux versions précédentes de PCI Express, la correction d’erreur directe est utilisée pour augmenter l’intégrité des données et PAM-4 est utilisé comme code de ligne afin que deux bits soient transférés par transfert. Avec un taux de transfert de données de 64 GT/s (Débit binaire brut), jusqu’à 252 Le Go/s est possible en configuration ×16. [88]

Le 24 février 2020, la spécification PCI Express 6.0 révision 0.5 (un “premier projet” avec tous les aspects architecturaux et exigences définis) a été publiée. [90]

Le 5 novembre 2020, la spécification PCI Express 6.0 révision 0.7 (un “projet complet” avec des spécifications électriques validées via des puces de test) a été publiée. [91]

Le 6 octobre 2021, la spécification PCI Express 6.0 révision 0.9 (un “projet final”) a été publiée. [92]

Le 11 janvier 2022, PCI-SIG a officiellement annoncé la publication de la spécification finale PCI-Express 6.0. [93]

Le codage PAM-4 entraîne un taux d’erreur sur les bits (BER) considérablement plus élevé de 10 -6 (contre 10 -12 précédemment), donc à la place du codage 128b / 130b, une correction d’erreur directe entrelacée (FEC) à 3 voies est utilisée en plus du contrôle de redondance cyclique (CRC). Un bloc d’ unité de contrôle de flux (FLIT) fixe de 256 octets transporte 242 octets de données, qui comprennent des paquets de niveau de transaction (TLP) de taille variable et une charge utile de couche de liaison de données (DLLP) ; les 14 octets restants sont réservés pour le CRC à 8 octets et le FEC à 6 octets. [94] [95] Code Gray à 3 voiesest utilisé en mode PAM-4/FLIT pour réduire le taux d’erreur ; l’interface ne passe pas à l’encodage NRZ et 128/130b même lors d’un recyclage à des débits de données inférieurs. [96] [97]

Extensions et orientations futures

Certains fournisseurs proposent des produits PCIe sur fibre, [98] [99] [100] avec des câbles optiques actifs (AOC) pour la commutation PCIe à distance accrue dans les tiroirs d’extension PCIe, [101] [85] ou dans des cas spécifiques où un pont PCIe transparent est préférable d’utiliser une norme plus courante (telle que InfiniBand ou Ethernet ) qui peut nécessiter un logiciel supplémentaire pour la prendre en charge.

Thunderbolt a été co-développé par Intel et Apple en tant qu’interface haute vitesse à usage général combinant une liaison PCIe logique avec DisplayPort et était à l’origine conçu comme une interface entièrement fibre, mais en raison des premières difficultés à créer une interconnexion fibre conviviale, presque toutes les implémentations sont des systèmes en cuivre. Une exception notable, le Sony VAIO Z VPC-Z2, utilise un port USB non standard avec un composant optique pour se connecter à un adaptateur d’affichage PCIe externe. Apple a été le principal moteur de l’adoption de Thunderbolt jusqu’en 2011, bien que plusieurs autres fournisseurs [102] aient annoncé de nouveaux produits et systèmes intégrant Thunderbolt. Thunderbolt 3 constitue la base de l’ USB4la norme.

La spécification Mobile PCIe (abrégé en M-PCIe ) permet à l’architecture PCI Express de fonctionner sur la technologie de couche physique M-PHY de MIPI Alliance . S’appuyant sur l’adoption généralisée déjà existante de M-PHY et sa conception à faible consommation d’énergie, Mobile PCIe permet aux appareils mobiles d’utiliser PCI Express. [103]

Processus de brouillon

Il existe 5 versions/points de contrôle principaux dans une spécification PCI-SIG : [104]

- Draft 0.3 (Concept) : cette version peut contenir peu de détails, mais décrit l’approche générale et les objectifs.

- Brouillon 0.5 (Premier brouillon) : cette version contient un ensemble complet d’exigences architecturales et doit répondre pleinement aux objectifs définis dans le brouillon 0.3.

- Brouillon 0.7 (Brouillon complet) : cette version doit avoir un ensemble complet d’exigences fonctionnelles et de méthodes définies, et aucune nouvelle fonctionnalité ne peut être ajoutée à la spécification après cette version. Avant la publication de ce projet, les spécifications électriques doivent avoir été validées via un silicium de test.

- Version 0.9 (version finale) : cette version permet aux sociétés membres de PCI-SIG d’effectuer un examen interne de la propriété intellectuelle, et aucune modification fonctionnelle n’est autorisée après cette version.

- 1.0 (version finale) : il s’agit de la spécification finale et définitive, et toute modification ou amélioration se fait respectivement par le biais de la documentation sur les errata et des avis de modification technique (ECN).

Historiquement, les premiers utilisateurs d’une nouvelle spécification PCIe commencent généralement à concevoir avec le brouillon 0.5, car ils peuvent construire en toute confiance leur logique d’application autour de la nouvelle définition de bande passante et souvent même commencer à développer pour toute nouvelle fonctionnalité de protocole. Cependant, au stade de l’ébauche 0.5, il existe encore une forte probabilité de changements dans l’implémentation réelle de la couche de protocole PCIe, de sorte que les concepteurs responsables du développement de ces blocs en interne peuvent être plus hésitants à commencer à travailler que ceux qui utilisent l’interface IP à partir de sources externes.

Résumé du protocole matériel

La liaison PCIe est construite autour de couples unidirectionnels dédiés de connexions série (1 bit) point à point appelées voies . Cela contraste fortement avec la connexion PCI antérieure, qui est un système basé sur un bus où tous les périphériques partagent le même bus parallèle bidirectionnel, 32 bits ou 64 bits.

PCI Express est un protocole en couches composé d’une couche de transaction , d’une couche de liaison de données et d’une couche physique . La couche de liaison de données est subdivisée pour inclure une sous-couche de contrôle d’accès au support (MAC). La couche physique est subdivisée en sous-couches logiques et électriques. La sous-couche logique physique contient une sous-couche de codage physique (PCS). Les termes sont empruntés au modèle de protocole de réseau IEEE 802 .

Couche physique

| Voies | Épingles | Longueur | ||

|---|---|---|---|---|

| Total | Variable | Total | Variable | |

| 0 ×1 | 2×18 = 0 36 [105] | 2× 0 7 = 0 14 | 25 millimètres | 0 7,65 mm |

| 0 ×4 | 2×32 = 0 64 | 2×21 = 0 42 | 39 millimètres | 21,65 millimètres |

| 0 ×8 | 2×49 = 0 98 | 2×38 = 0 76 | 56 millimètres | 38,65 millimètres |

| ×16 | 2×82 = 164 | 2×71 = 142 | 89 millimètres | 71,65 millimètres |

La spécification de la couche physique PCIe ( PHY , PCIEPHY , PCI Express PHY ou PCIe PHY ) est divisée en deux sous-couches, correspondant aux spécifications électriques et logiques. La sous-couche logique est parfois divisée en une sous-couche MAC et un PCS, bien que cette division ne fasse pas officiellement partie de la spécification PCIe. Une spécification publiée par Intel, la PHY Interface for PCI Express (PIPE), [106] définit le partitionnement fonctionnel MAC/PCS et l’interface entre ces deux sous-couches. La spécification PIPE identifie également la couche PMA ( Physical Media Attachment) , qui comprend le sérialiseur/désérialiseur (SerDes).et autres circuits analogiques ; cependant, étant donné que les implémentations de SerDes varient considérablement d’un fournisseur d’ ASIC à l’autre , PIPE ne spécifie pas d’interface entre le PCS et le PMA.

Au niveau électrique, chaque voie est constituée de deux paires différentielles unidirectionnelles fonctionnant à 2,5, 5, 8, 16 ou 32 Gbit /s, selon les capacités négociées. La transmission et la réception sont des paires différentielles distinctes, pour un total de quatre fils de données par voie.

Une connexion entre deux périphériques PCIe est connue sous le nom de liaison et est constituée d’un ensemble d’une ou plusieurs voies . Tous les appareils doivent au minimum prendre en charge une liaison à voie unique (×1). Les appareils peuvent éventuellement prendre en charge des liaisons plus larges composées de 32 voies maximum. [107] [108] Cela permet une très bonne compatibilité de deux manières :

- Une carte PCIe s’adapte physiquement (et fonctionne correctement) dans n’importe quel emplacement qui est au moins aussi grand qu’il l’est (par exemple, une carte de taille ×1 fonctionne dans n’importe quel emplacement de taille) ;

- Un emplacement de grande taille physique (par exemple, × 16) peut être câblé électriquement avec moins de voies (par exemple, × 1, × 4, × 8 ou × 12) tant qu’il fournit les connexions à la terre requises par l’emplacement physique plus grand Taille.

Dans les deux cas, PCIe négocie le plus grand nombre de voies mutuellement prises en charge. De nombreuses cartes graphiques, cartes mères et versions de BIOS sont vérifiées pour prendre en charge la connectivité ×1, ×4, ×8 et ×16 sur la même connexion.

La largeur d’un connecteur PCIe est de 8,8 mm, tandis que la hauteur est de 11,25 mm et la longueur est variable. La section fixe du connecteur mesure 11,65 mm de long et contient deux rangées de 11 broches chacune (22 broches au total), tandis que la longueur de l’autre section est variable en fonction du nombre de voies. Les broches sont espacées de 1 mm et l’épaisseur de la carte entrant dans le connecteur est de 1,6 mm. [109] [110]

Transmission de données

PCIe envoie tous les messages de contrôle, y compris les interruptions, sur les mêmes liens utilisés pour les données. Le protocole série ne peut jamais être bloqué, de sorte que la latence est toujours comparable à celle du PCI conventionnel, qui dispose de lignes d’interruption dédiées. Lorsque le problème du partage IRQ des interruptions basées sur les broches est pris en compte et que les interruptions signalées par message (MSI) peuvent contourner un APIC d’E / S et être livrées directement au CPU, les performances MSI finissent par être nettement meilleures. [111]

Les données transmises sur des liaisons à plusieurs voies sont entrelacées, ce qui signifie que chaque octet successif est envoyé sur des voies successives. La spécification PCIe fait référence à cet entrelacement en tant que segmentation des données . Tout en nécessitant une complexité matérielle importante pour synchroniser (ou redresser ) les données entrelacées entrantes, la répartition peut réduire considérablement la latence du n ième octet sur une liaison. Bien que les voies ne soient pas étroitement synchronisées, il y a une limite à l’ inclinaison voie à voie de 20/8/6 ns pour 2,5/5/8 GT/s afin que les tampons matériels puissent réaligner les données réparties. [112] En raison des exigences de remplissage, la répartition ne réduit pas nécessairement la latence des petits paquets de données sur une liaison.

Comme pour les autres protocoles de transmission série à haut Débit, l’horloge est intégrée au signal. Au niveau physique, PCI Express 2.0 utilise le schéma de codage 8b/10b [46] (code de ligne) pour garantir que les chaînes de chiffres consécutifs identiques (zéros ou uns) sont limitées en longueur. Ce codage a été utilisé pour empêcher le récepteur de perdre la trace de l’emplacement des bords de bit. Dans ce schéma de codage, tous les huit bits de charge utile (non codés) de données sont remplacés par 10 bits (codés) de données de transmission, ce qui entraîne une surcharge de 20 % dans la bande passante électrique. Pour améliorer la bande passante disponible, PCI Express version 3.0 utilise à la place l’encodage 128b/130b (1,54 % de surcoût). Codage de lignelimite la longueur d’exécution des chaînes de chiffres identiques dans les flux de données et garantit que le récepteur reste synchronisé avec l’émetteur via la récupération d’horloge .

Un équilibre souhaitable (et donc une densité spectrale ) des bits 0 et 1 dans le flux de données est obtenu en effectuant un XOR sur un polynôme binaire connu en tant que ” brouilleur ” sur le flux de données dans une topologie de rétroaction. Comme le polynôme de brouillage est connu, les données peuvent être récupérées en appliquant le XOR une seconde fois. Les étapes d’embrouillage et de désembrouillage sont exécutées dans le matériel.

Couche de liaison de données

La couche de liaison de données exécute trois services vitaux pour la liaison PCIe :

- séquencer les paquets de la couche transaction (TLP) qui sont générés par la couche transaction,

- assurer une livraison fiable des TLP entre deux terminaux via un protocole d’accusé de réception ( signalisation ACK et NAK ) qui nécessite explicitement la relecture des TLP non acquittés/mauvais,

- initialiser et gérer les crédits de contrôle de flux

Du côté émission, la couche liaison de données génère un numéro de séquence incrémenté pour chaque TLP sortant. Il sert d’étiquette d’identification unique pour chaque TLP transmis et est inséré dans l’en-tête du TLP sortant. Un code de contrôle de redondance cyclique de 32 bits (appelé dans ce contexte Link CRC ou LCRC) est également ajouté à la fin de chaque TLP sortant.

Du côté réception, le LCRC et le numéro de séquence du TLP reçu sont tous deux validés dans la couche liaison. Si la vérification LCRC échoue (indiquant une erreur de données) ou si le numéro de séquence est hors plage (non consécutif à partir du dernier TLP valide reçu), alors le mauvais TLP, ainsi que tous les TLP reçus après le mauvais TLP, sont considérés comme invalides et rejetés. Le récepteur envoie un message d’accusé de réception négatif (NAK) avec le numéro de séquence du TLP invalide, demandant la retransmission de tous les TLP vers l’avant de ce numéro de séquence. Si le TLP reçu réussit le contrôle LCRC et a le numéro de séquence correct, il est traité comme valide. Le récepteur de liaison incrémente le numéro de séquence (qui suit le dernier bon TLP reçu) et transmet le TLP valide à la couche de transaction du récepteur. Un message ACK est envoyé à l’émetteur distant,

Si l’émetteur reçoit un message NAK, ou si aucun accusé de réception (NAK ou ACK) n’est reçu jusqu’à l’expiration d’une période de temporisation, l’émetteur doit retransmettre tous les TLP qui n’ont pas d’accusé de réception positif (ACK). À moins d’un dysfonctionnement persistant de l’appareil ou du support de transmission, la couche liaison présente une connexion fiable à la couche transaction, puisque le protocole de transmission assure la livraison des TLP sur un support non fiable.

En plus d’envoyer et de recevoir des TLP générés par la couche de transaction, la couche de liaison de données génère et consomme également des paquets de couche de liaison de données (DLLP). Les signaux ACK et NAK sont communiqués via les DLLP, tout comme certains messages de gestion de l’alimentation et les informations de crédit de contrôle de flux (au nom de la couche de transaction).

En pratique, le nombre de TLP en vol non acquittés sur la liaison est limité par deux facteurs : la taille du tampon de relecture de l’émetteur (qui doit stocker une copie de tous les TLP transmis jusqu’à ce que le récepteur distant les ACK) et le contrôle de flux. crédits délivrés par le récepteur à un émetteur. PCI Express exige que tous les récepteurs émettent un nombre minimum de crédits, pour garantir qu’un lien permet d’envoyer des TLP PCIConfig et des TLP de message.

Couche transactionnelle

PCI Express implémente des transactions fractionnées (transactions avec demande et réponse séparées par le temps), permettant au lien de transporter un autre trafic pendant que le périphérique cible collecte des données pour la réponse.

PCI Express utilise un contrôle de flux basé sur le crédit. Dans ce schéma, un appareil annonce un montant initial de crédit pour chaque tampon reçu dans sa couche de transaction. L’appareil à l’extrémité opposée du lien, lors de l’envoi de transactions à cet appareil, compte le nombre de crédits que chaque TLP consomme sur son compte. L’appareil émetteur ne peut transmettre un TLP que lorsque cela ne fait pas en sorte que son compte de crédit consommé dépasse sa limite de crédit. Lorsque l’appareil récepteur termine le traitement du TLP à partir de sa mémoire tampon, il signale un retour de crédits à l’appareil émetteur, ce qui augmente la limite de crédit du montant restauré. Les compteurs de crédit sont des compteurs modulaires, et la comparaison des crédits consommés à la limite de crédit nécessite une arithmétique modulaire. L’avantage de ce schéma (par rapport à d’autres méthodes telles que les états d’attente ou les protocoles de transfert basés sur la poignée de main) est que la latence du retour de crédit n’affecte pas les performances, à condition que la limite de crédit ne soit pas atteinte. Cette hypothèse est généralement satisfaite si chaque périphérique est conçu avec des tailles de mémoire tampon adéquates.

PCIe 1.x est souvent cité pour prendre en charge un Débit de données de 250 Mo/s dans chaque direction, par voie. Ce chiffre est un calcul à partir du Débit de signalisation physique (2,5 gigabauds ) divisé par la surcharge de codage (10 bits par octet). Cela signifie qu’une carte PCIe à seize voies (×16) serait alors théoriquement capable de 16 × 250 Mo/s = 4 Go/s dans chaque direction. Bien que cela soit correct en termes d’octets de données, des calculs plus significatifs sont basés sur le taux de charge utile de données utilisable, qui dépend du profil du trafic, qui est fonction de l’application de haut niveau (logiciel) et des niveaux de protocole intermédiaires.

Comme d’autres systèmes d’interconnexion série à haut Débit de données, PCIe a une surcharge de protocole et de traitement en raison de la robustesse de transfert supplémentaire (CRC et accusés de réception). Les longs transferts unidirectionnels continus (tels que ceux typiques des contrôleurs de stockage hautes performances) peuvent approcher > 95 % du Débit de données brutes (voie) de PCIe. Ces transferts bénéficient également le plus d’un nombre accru de voies (×2, ×4, etc.). Mais dans des applications plus typiques (telles qu’un contrôleur USB ou Ethernet ), le profil de trafic se caractérise par de courts paquets de données avec des accusés de réception fréquents. [113]Ce type de trafic réduit l’efficacité de la liaison, en raison de la surcharge due à l’analyse des paquets et aux interruptions forcées (soit dans l’interface hôte du périphérique, soit dans le processeur du PC). Étant un protocole pour les appareils connectés à la même carte de circuit imprimé , il ne nécessite pas la même tolérance aux erreurs de transmission qu’un protocole de communication sur de plus longues distances, et donc, cette perte d’efficacité n’est pas particulière à PCIe.

Efficacité du lien

Comme pour toutes les liaisons de communication “de type réseau”, une partie de la bande passante “brute” est consommée par la surcharge du protocole : [114]

Une voie PCIe 1.x par exemple offre un Débit de données au-dessus de la couche physique de 250 Mo/s (simplex). Il ne s’agit pas de la bande passante de la charge utile mais de la bande passante de la couche physique – une voie PCIe doit transporter des informations supplémentaires pour une fonctionnalité complète. [114]

| Couche | PHY | Couche de liaison de données | Transaction | Couche de liaison de données | PHY | ||

|---|---|---|---|---|---|---|---|

| Données | Démarrer | Séquence | Entête | Charge utile | CREC | LCRC | Finir |

| Taille (octets) | 1 | 2 | 12 ou 16 | 0 à 4096 | 4 (facultatif) | 4 | 1 |

La surcharge Gen2 est alors de 20, 24 ou 28 octets par transaction. [ clarification nécessaire ] [ citation nécessaire ]

| Couche | G3 PHY | Couche de liaison de données | Couche transactionnelle | Couche de liaison de données | ||

|---|---|---|---|---|---|---|

| Données | Démarrer | Séquence | Entête | Charge utile | CREC | LCRC |

| Taille (octets) | 4 | 2 | 12 ou 16 | 0 à 4096 | 4 (facultatif) | 4 |

L’overhead Gen3 est alors de 22, 26 ou 30 octets par transaction. [ clarification nécessaire ] [ citation nécessaire ]

Le Packet Efficiency = Payload ( Payload + Overhead ) {displaystyle {text{Efficacité des paquets}}={frac {text{Payload}}{left({text{Payload}}+{text{Overhead}}right)}}}

pour une charge utile de 128 octets est de 86 % et de 98 % pour une charge utile de 1 024 octets. Pour les petits accès comme les paramètres de registre (4 octets), l’efficacité chute jusqu’à 16 %. [ citation nécessaire ]

La taille de charge utile maximale (MPS) est définie sur tous les appareils en fonction du plus petit maximum sur n’importe quel appareil de la chaîne. Si un appareil a un MPS de 128 octets, tous les appareils de l’arborescence doivent définir leur MPS sur 128 octets. Dans ce cas, le bus aura une efficacité maximale de 86 % pour les écritures. [114] : 3

Applications

Asus Nvidia GeForce GTX 650 Ti, une carte graphique PCI Express 3.0 ×16

Asus Nvidia GeForce GTX 650 Ti, une carte graphique PCI Express 3.0 ×16

La Nvidia GeForce GTX 1070, une carte graphique PCI Express 3.0 ×16.

La Nvidia GeForce GTX 1070, une carte graphique PCI Express 3.0 ×16.

Carte réseau Gigabit Ethernet Intel 82574L , une carte PCI Express ×1

Carte réseau Gigabit Ethernet Intel 82574L , une carte PCI Express ×1

Un contrôleur SATA 3.0 basé sur Marvell , en tant que carte PCI Express ×1

Un contrôleur SATA 3.0 basé sur Marvell , en tant que carte PCI Express ×1

PCI Express fonctionne dans les applications grand public, serveur et industrielles, en tant qu’interconnexion au niveau de la carte mère (pour relier les périphériques montés sur la carte mère), en tant qu’interconnexion de fond de panier passive et en tant qu’interface de carte d’extension pour les cartes d’extension .

Dans pratiquement tous les PC modernes (à partir de 2012 [update]), des ordinateurs portables et ordinateurs de bureau grand public aux serveurs de données d’entreprise, le bus PCIe sert d’interconnexion principale au niveau de la carte mère, connectant le processeur du système hôte aux périphériques intégrés (circuits intégrés montés en surface) et périphériques supplémentaires (cartes d’extension). Dans la plupart de ces systèmes, le bus PCIe coexiste avec un ou plusieurs bus PCI hérités, pour une compatibilité descendante avec le grand nombre de périphériques PCI hérités.

Depuis 2013 [update], PCI Express a remplacé AGP comme interface par défaut pour les cartes graphiques sur les nouveaux systèmes. Presque tous les modèles de cartes graphiques commercialisés depuis 2010 par AMD (ATI) et Nvidia utilisent le PCI Express. Nvidia utilise le transfert de données à large bande passante de PCIe pour sa technologie Scalable Link Interface (SLI), qui permet à plusieurs cartes graphiques du même chipset et du même numéro de modèle de fonctionner en tandem, permettant des performances accrues. [ citation nécessaire ] AMD a également développé un système multi-GPU basé sur PCIe appelé CrossFire . [ citation nécessaire ]AMD, Nvidia et Intel ont publié des chipsets de carte mère prenant en charge jusqu’à quatre emplacements PCIe × 16, permettant des configurations de cartes tri-GPU et quad-GPU.

GPU externes

Théoriquement, le PCIe externe pourrait donner à un ordinateur portable la puissance graphique d’un ordinateur de bureau, en connectant un ordinateur portable à n’importe quelle Carte vidéo de bureau PCIe (enfermée dans son propre boîtier externe, avec alimentation et refroidissement) ; cela est possible avec une interface ExpressCard ou Thunderbolt . Une interface ExpressCard fournit des débits binaires de 5 Gbit/s (Débit de 0,5 Go/s), tandis qu’une interface Thunderbolt fournit des débits binaires allant jusqu’à 40 Gbit/s (Débit de 5 Go/s).

En 2006, Nvidia a développé la famille de GPU PCIe externes Quadro Plex qui peut être utilisée pour des applications graphiques avancées pour le marché professionnel. [115] Ces cartes vidéo nécessitent un emplacement PCI Express x8 ou x16 pour la carte côté hôte, qui se connecte au Plex via un VHDCI transportant huit voies PCIe. [116]

En 2008, AMD a annoncé la technologie ATI XGP , basée sur un système de câblage propriétaire compatible avec les transmissions de signaux PCIe ×8. [117] Ce connecteur est disponible sur les ordinateurs portables Fujitsu Amilo et Acer Ferrari One. Fujitsu a lancé son boîtier AMILO GraphicBooster pour XGP peu de temps après. [118] Vers 2010, Acer a lancé la station d’accueil graphique Dynavivid pour XGP. [119]

En 2010, des concentrateurs de cartes externes ont été introduits qui peuvent se connecter à un ordinateur portable ou de bureau via un emplacement PCI ExpressCard. Ces concentrateurs peuvent accepter des cartes graphiques de taille normale. Les exemples incluent MSI GUS, [120] ViDock de Village Instrument, [121] la station Asus XG , l’adaptateur Bplus PE4H V3.2, [122] ainsi que des appareils de bricolage plus improvisés. [123] Cependant, ces solutions sont limitées par la taille (souvent seulement ×1) et la version de l’emplacement PCIe disponible sur un ordinateur portable.

L’interface Intel Thunderbolt a fourni une nouvelle option pour se connecter avec une carte PCIe en externe. Magma a sorti l’ExpressBox 3T, qui peut contenir jusqu’à trois cartes PCIe (deux à ×8 et une à ×4). [124] MSI a également lancé le Thunderbolt GUS II, un châssis PCIe dédié aux cartes vidéo. [125] D’autres produits tels que l’Echo Express de Sonnet [126] et le mLink de mLogic sont des châssis Thunderbolt PCIe dans un facteur de forme plus petit. [127]

En 2017, des concentrateurs de cartes externes plus complets ont été introduits, tels que le Razer Core, qui possède une interface PCIe × 16 pleine longueur. [128]

Périphériques de stockage

Un SSD OCZ RevoDrive , une carte PCI Express x4 pleine hauteur

Un SSD OCZ RevoDrive , une carte PCI Express x4 pleine hauteur

Le protocole PCI Express peut être utilisé comme interface de données pour les périphériques de mémoire flash , tels que les cartes mémoire et les disques SSD.

La carte XQD est un format de carte mémoire utilisant PCI Express, développé par la CompactFlash Association, avec des taux de transfert allant jusqu’à 1 Go/s. [129]

De nombreux SSD hautes performances de classe entreprise sont conçus comme des cartes contrôleur RAID PCI Express . [ citation nécessaire ] Avant que NVMe ne soit normalisé, bon nombre de ces cartes utilisaient des interfaces propriétaires et des pilotes personnalisés pour communiquer avec le système d’exploitation ; ils avaient des taux de transfert beaucoup plus élevés (plus de 1 Go/s) et des IOPS (plus d’un million d’opérations d’E/S par seconde) par rapport aux disques Serial ATA ou SAS . [ quantifier ] [130] [131]Par exemple, en 2011, OCZ et Marvell ont co-développé un contrôleur de disque SSD PCI Express natif pour un emplacement PCI Express 3.0 × 16 avec une capacité maximale de 12 To et une performance de transferts séquentiels jusqu’à 7,2 Go/s et jusqu’à 2,52 millions IOPS dans les transferts aléatoires. [132] [ pertinence remise en question ]

SATA Express était une interface permettant de connecter des SSD via des ports compatibles SATA, fournissant éventuellement plusieurs voies PCI Express en tant que connexion PCI Express pure au périphérique de stockage connecté. [133] M.2 est une spécification pour les cartes d’extension d’ordinateur montées en interne et les connecteurs associés, qui utilise également plusieurs voies PCI Express. [134]

Les périphériques de stockage PCI Express peuvent implémenter à la fois l’interface logique AHCI pour la rétrocompatibilité et l’interface logique NVM Express pour des opérations d’E/S beaucoup plus rapides grâce à l’utilisation du parallélisme interne offert par ces périphériques. Les SSD de classe entreprise peuvent également implémenter SCSI sur PCI Express . [135]

Interconnexion de cluster

Certaines applications de centre de données (telles que les grands clusters d’ordinateurs ) nécessitent l’utilisation d’interconnexions à fibre optique en raison des limitations de distance inhérentes au câblage en cuivre. En règle générale, une norme orientée réseau telle qu’Ethernet ou Fibre Channel suffit pour ces applications, mais dans certains cas, la surcharge introduite par les protocoles routables n’est pas souhaitable et une interconnexion de niveau inférieur, telle que InfiniBand , RapidIO ou NUMAlink est nécessaire. Les normes de bus local telles que PCIe et HyperTransport peuvent en principe être utilisées à cette fin, [136] mais à partir de 2015[update], les solutions ne sont disponibles que chez des fournisseurs de niche tels que Dolphin ICS et TTTech Auto.

Protocoles concurrents

Parmi les autres normes de communication basées sur des architectures série à large bande passante, citons InfiniBand , RapidIO , HyperTransport , Intel QuickPath Interconnect et Mobile Industry Processor Interface (MIPI). Les différences sont basées sur les compromis entre la flexibilité et l’extensibilité par rapport à la latence et à la surcharge. Par exemple, rendre le système enfichable à chaud, comme avec Infiniband mais pas PCI Express, nécessite que le logiciel suive les changements de topologie du réseau. [ citation nécessaire ]

Un autre exemple consiste à raccourcir les paquets pour réduire la latence (comme cela est nécessaire si un bus doit fonctionner comme une interface mémoire). Des paquets plus petits signifient que les en-têtes de paquet consomment un pourcentage plus élevé du paquet, diminuant ainsi la bande passante effective. Des exemples de protocoles de bus conçus à cet effet sont RapidIO et HyperTransport. [ citation nécessaire ]

PCI Express se situe quelque part au milieu, ciblé par sa conception comme une interconnexion de système ( bus local ) plutôt qu’une interconnexion de périphérique ou un protocole de réseau routé. De plus, son objectif de conception de transparence logicielle contraint le protocole et augmente quelque peu sa latence. [ citation nécessaire ]

Des retards dans les implémentations de PCIe 4.0 ont conduit au consortium Gen-Z , à l’effort CCIX et à une interface de processeur d’accélération cohérente (CAPI) ouverte, tous annoncés d’ici la fin de 2016. [137]

Le 11 mars 2019, Intel a présenté Compute Express Link (CXL) , un nouveau bus d’interconnexion, basé sur l’infrastructure de couche physique PCI Express 5.0. Les promoteurs initiaux de la spécification CXL comprenaient : Alibaba , Cisco , Dell EMC , Facebook , Google , HPE , Huawei , Intel et Microsoft . [138]

Liste des intégrateurs

La liste des intégrateurs PCI-SIG répertorie les produits fabriqués par les sociétés membres PCI-SIG qui ont réussi les tests de conformité. La liste comprend des commutateurs, des ponts, des cartes réseau, des disques SSD, etc. [139]

Voir également

-

![icon]()

![icon]() Portail électronique

Portail électronique

- Gestion de l’alimentation à l’état actif (ASPM)

- PCI conventionnel

- Espace de configuration PCI

- PCI-X

- PCI/104-Express

- PCIe/104

- Complexe racinaire

- Sortie vidéo numérique série (SDVO)

- Liste des débits binaires de l’appareil § Bus principaux

- OPCe

Remarques

- ^ Les commutateurs peuvent créer plusieurs points de terminaison à partir d’un seul pour permettre le partage avec plusieurs appareils.

- ^ Le connecteur d’alimentation Serial ATA de la carte est présent car les ports USB 3.0 nécessitent plus d’énergie que le bus PCI Express ne peut en fournir. Le plus souvent, un connecteur d’alimentation Molex à 4 broches est utilisé.

Références

- ^ Mayhew, D.; Krishnan, V. (août 2003). “Commutation PCI express et avancée: voie évolutive vers la construction d’interconnexions de prochaine génération”. 11e symposium sur les interconnexions à haute performance, 2003. Actes . p. 21–29. doi : 10.1109/CONECT.2003.1231473 . ISBN 0-7695-2012-X. S2CID 7456382 .

- ^ “Définition de PCI Express” . PCMag .

- ^ Zhang, Yanmin; Nguyen, T Long (juin 2007). “Activer le rapport d’erreur avancé PCI Express dans le noyau” (PDF) . Actes du symposium Linux . Projet Fedora. Archivé de l’original (PDF) le 10 mars 2016 . Récupéré le 8 mai 2012 .

- ^ https://www.hyperstone.com Flash Memory Form Factors – The Fundamentals of Reliable Flash Storage, récupéré le 19 avril 2018

- ^ un bc Ravi Budruk (21 août 2007). “Les bases de PCI Express” . PCI-SIG . Archivé de l’original (PDF) le 15 juillet 2014 . Récupéré le 15 juillet 2014 .